Code: Alles auswählen

MIPSProblem: Ich kenne nicht jeden opcode vom mips. Fernuni hagen, beschreibt ihn komplett. Opcode jedes aber nicht dabei. Abhilfe schaffen kann Mars. Man muss jeden Befehl einzeln anschauen. Gerade keinen bock

Auch nicht darauf, aus einem 1 Bit Register 32 zu machen. Das ist gerade jetzt kein spass

Nicht heute abend. Morgen früh vielleicht. Bevor man die opcodes anfängt, halt sagen sie nichts. Die braucht man nicht so sehr, das wichtige sind

Code: Alles auswählen

funcCode: Alles auswählen

rt, rs, rdNatürlich läuft auf dem kein Linux aber der Schritt ist nicht so weit

Ich denke schon, dass ich jetzt anfange, ich muss nur kurz was anderes tun

Und vergessen sie die Diskussion über mips und risc-v. Mein Vorschlag, wir schaffen einen, der geht. Und dann diskutieren wir die weiteren Details..

Ökonomischer ansatz: Erst haben, dann können wir due Kultur aufleben lassen. Was ihr Getränk betrifft. Leute, die darüber reden und es unterscheiden, aber nie gemacht haben, sind schlimmer wie das Gegenteil.

Wenn sie Computersysteme i/ii richtig gelesen haben, wissen sie wie es geht.

Ich denke, es ist tatsächlich so, dass ich erst wissen möchte, wie ich aus 1 Bit 32 mache. Was

Code: Alles auswählen

PORT MAPIch glaube das Schlagwort heisst,

Code: Alles auswählen

GENERIC MAPIch sehe, es geht wohl mit einer

Code: Alles auswählen

FORCode: Alles auswählen

FORDoch, ich habe es raus gekriegt, es ist beides

Code: Alles auswählen

FORCode: Alles auswählen

GENERATEhttps://l.facebook.com/l.php?u=https%3A ... wLzq982t5w

Code: Alles auswählen

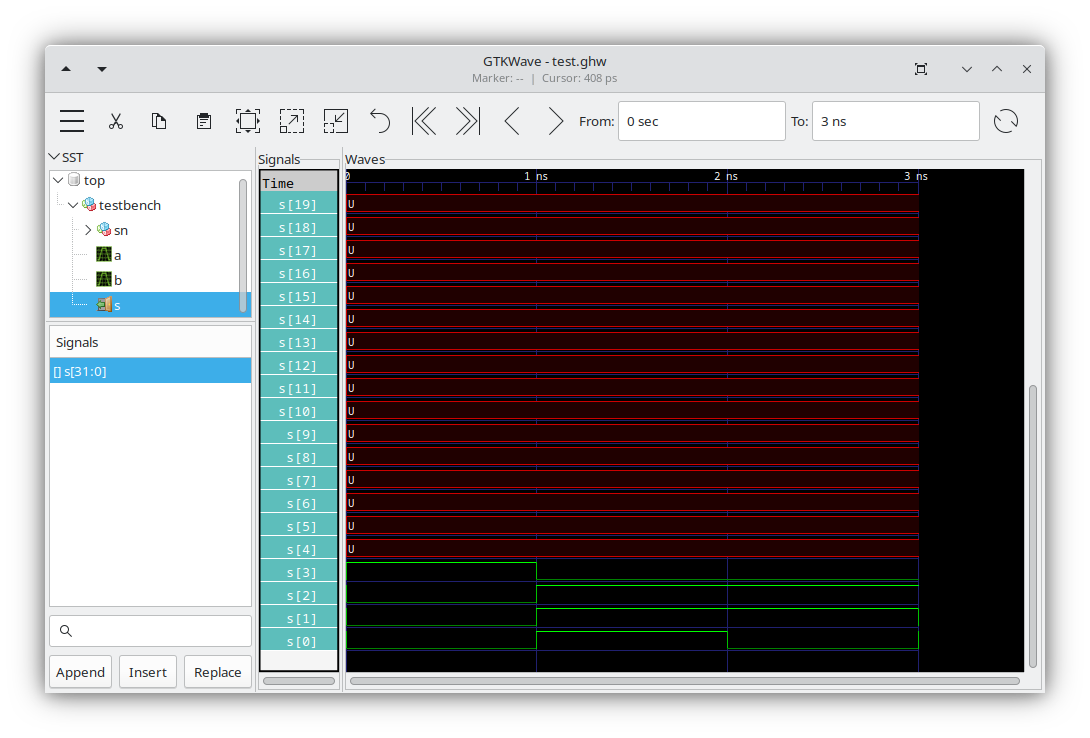

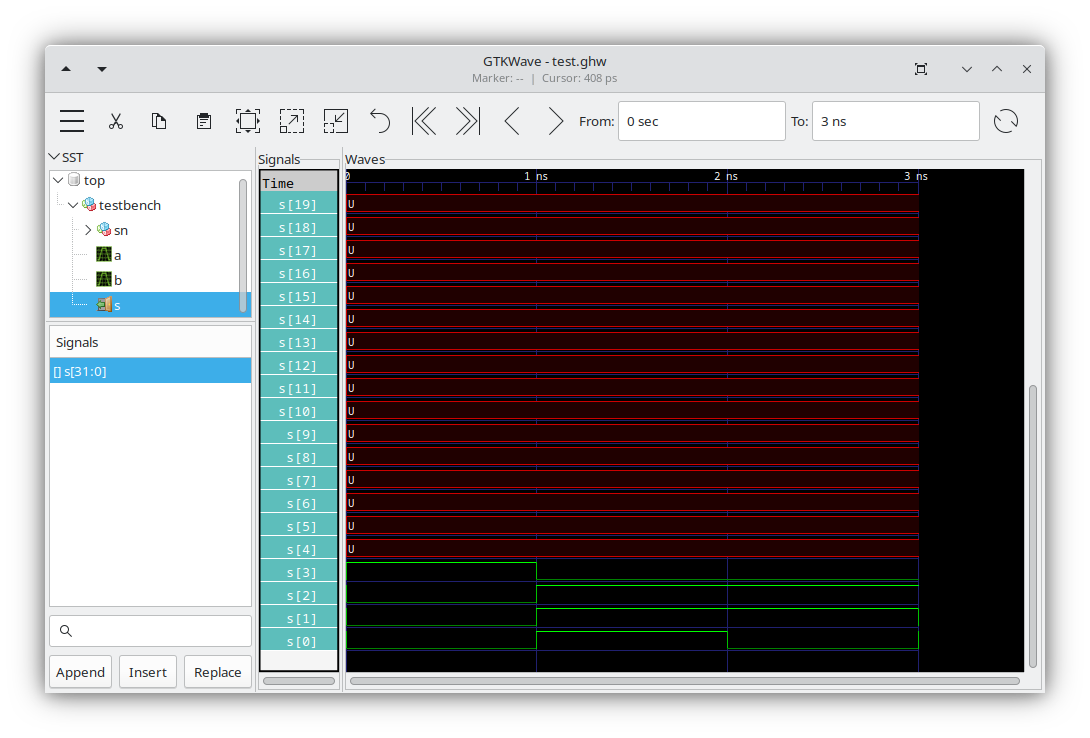

-- Ah geil, es hat funktioniert!!!

-- Es tut!!!

-- Ich probiere jetzt einen Ripple Carry Adder

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz is

port (

a, b: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz is

begin

y <= a and b;

end;

library ieee;

use ieee.std_logic_1164.all;

entity meingrosseschaltnetz is

port (

y: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture verhalten of meingrosseschaltnetz is

component meinschaltnetz

port (

a, b: in std_logic;

y: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

sn: meinschaltnetz PORT MAP (b=>b(i), a=>a(i), y=>y(i));

end generate;

end;

Code: Alles auswählen

-- Scheint mit dem Ripple Carry Adder zu funktionierern

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end;

architecture verhalten of fulladder is

begin

s <= a xor b xor c;

u <= (a and b) or ((a or b) and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarryadder is

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture verhalten of ripplecarryadder is

component fulladder

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end component;

signal c : std_logic_vector (31 downto 0);

signal u : std_logic_vector (31 downto 0);

begin

c(0) <= '0';

add1: fulladder PORT MAP (c=>c(0),b=>b(0),a=>a(0),s=>s(0),u=>u(0));

l1:

for i in 1 to 31 generate

sn: fulladder PORT MAP (c=>u(i-1),b=>b(i),a=>a(i),s=>s(i),u=>u(i));

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbench is

port (

s: out std_logic_vector (31 downto 0)

);

end;

architecture verhalten of testbench is

component ripplecarryadder

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end component;

signal b, a: std_logic_vector (31 downto 0);

begin

sn: ripplecarryadder PORT MAP (b=>b, a=>a, s=>s);

a (0) <= '1' after 0 ns, '0' after 1 ns , '1' after 2 ns, '0' after 3 ns;

b (0) <= '1' after 0 ns;

a (1) <= '1' after 0 ns, '0' after 2 ns;

b (1) <= '0' after 0 ns;

a (2) <= '0' after 0 ns;

b (2) <= '1' after 0 ns;

a (3) <= '1' after 0 ns;

b (3) <= '1' after 0 ns;

end;

Code: Alles auswählen

a (0) <= '1' after 0 ns, '0' after 1 ns , '1' after 2 ns, '0' after 3 ns;

b (0) <= '1' after 0 ns;

a (1) <= '1' after 0 ns, '0' after 2 ns;

b (1) <= '0' after 0 ns;

a (2) <= '0' after 0 ns;

b (2) <= '1' after 0 ns;

a (3) <= '1' after 0 ns;

b (3) <= '1' after 0 ns;

-- wenn man das anguckt und das bild, dann scheint das gut zu funktionieren