Nächste Seite: Re: JavaScript, Python Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

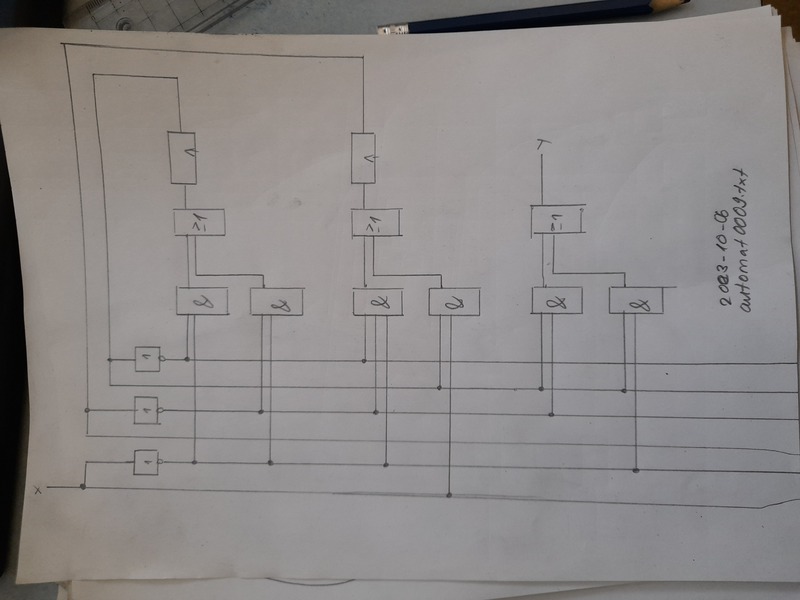

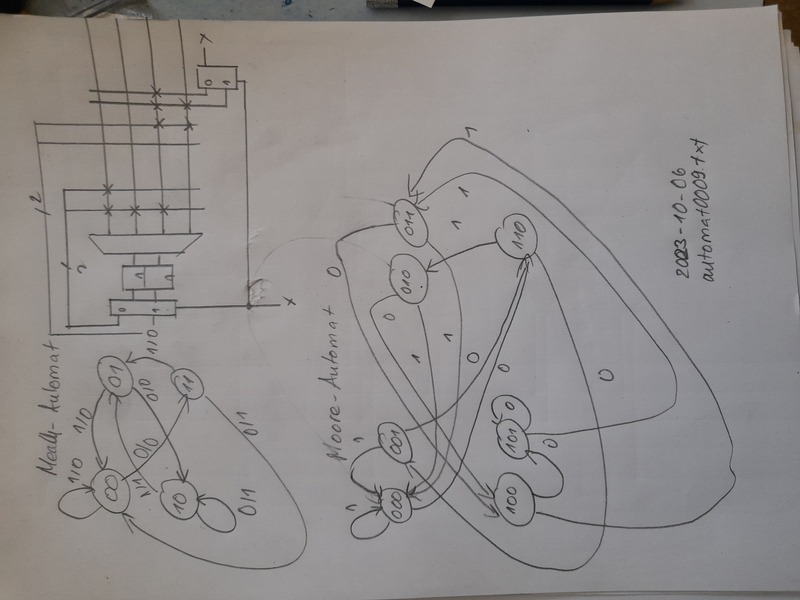

b a x b a y 0 0 0 0 1 1 0 1 0 0 1 0 0 0 2 0 1 0 1 0 0 3 0 1 1 0 0 0 4 1 0 0 1 0 1 5 1 0 1 0 1 1 6 1 1 0 0 0 1 7 1 1 1 0 1 0 b a x b 0 0 0 0 1 1 0 0 1 0 2 0 1 0 1 3 0 1 1 0 4 1 0 0 1 5 1 0 1 0 6 1 1 0 0 7 1 1 1 0 b a x a 0 0 0 0 1 1 0 0 1 0 2 0 1 0 0 3 0 1 1 0 4 1 0 0 0 5 1 0 1 1 6 1 1 0 0 7 1 1 1 1 b a x y 0 0 0 0 0 1 0 0 1 0 2 0 1 0 0 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0 b a x b 0 0 0 0 1 2 0 1 0 1 4 1 0 0 1 b a x a 0 0 0 0 1 5 1 0 1 1 7 1 1 1 1 b a x y 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 b a x b Gruppe 0: 0 0 0 0 1 Gruppe 1: 2 0 1 0 1 4 1 0 0 1 b a x a Gruppe 0: 0 0 0 0 1 Gruppe 2: 5 1 0 1 1 Gruppe 3: 7 1 1 1 1 b a x y Gruppe 1: 4 1 0 0 1 Gruppe 2: 5 1 0 1 1 6 1 1 0 1 b a x b Gruppe 0: 0 0 0 0 1 Gruppe 1: 2 0 1 0 1 4 1 0 0 1 0;2 0 - 0 0;4 - 0 0 b <= (not b and not x) or (not a and not x) b a x a Gruppe 0: 0 0 0 0 1 Gruppe 2: 5 1 0 1 1 Gruppe 3: 7 1 1 1 1 0 0 0 0 5;7 1 - 1 a <= (not b and not a and not x) or (b and x) b a x y Gruppe 1: 4 1 0 0 1 Gruppe 2: 5 1 0 1 1 6 1 1 0 1 4;5 1 0 - 4;6 1 - 0 y <= (b and not a) or (b and not x) b <= (not b and not x) or (not a and not x) a <= (not b and not a and not x) or (b and x) y <= (b and not a) or (b and not x)

VHDL-Code:

entity automatenuebergangsschaltnetz is port ( bin, ain, x: in bit; bout, aout: out bit ); end; entity automatenausgangsschaltnetz is port ( bin, ain, x: in bit; y: out bit ); end; architecture verhalten of automatenuebergangsschaltnetz is begin bout <= (not bin and not x) or (not ain and not x); aout <= (not bin and not ain and not x) or (bin and x); end; architecture verhalten of automatenausgangsschaltnetz is begin y <= (bin and not ain) or (bin and not x); end;