Nächste Seite: Re: OK, let's Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: MySQL, Bash -

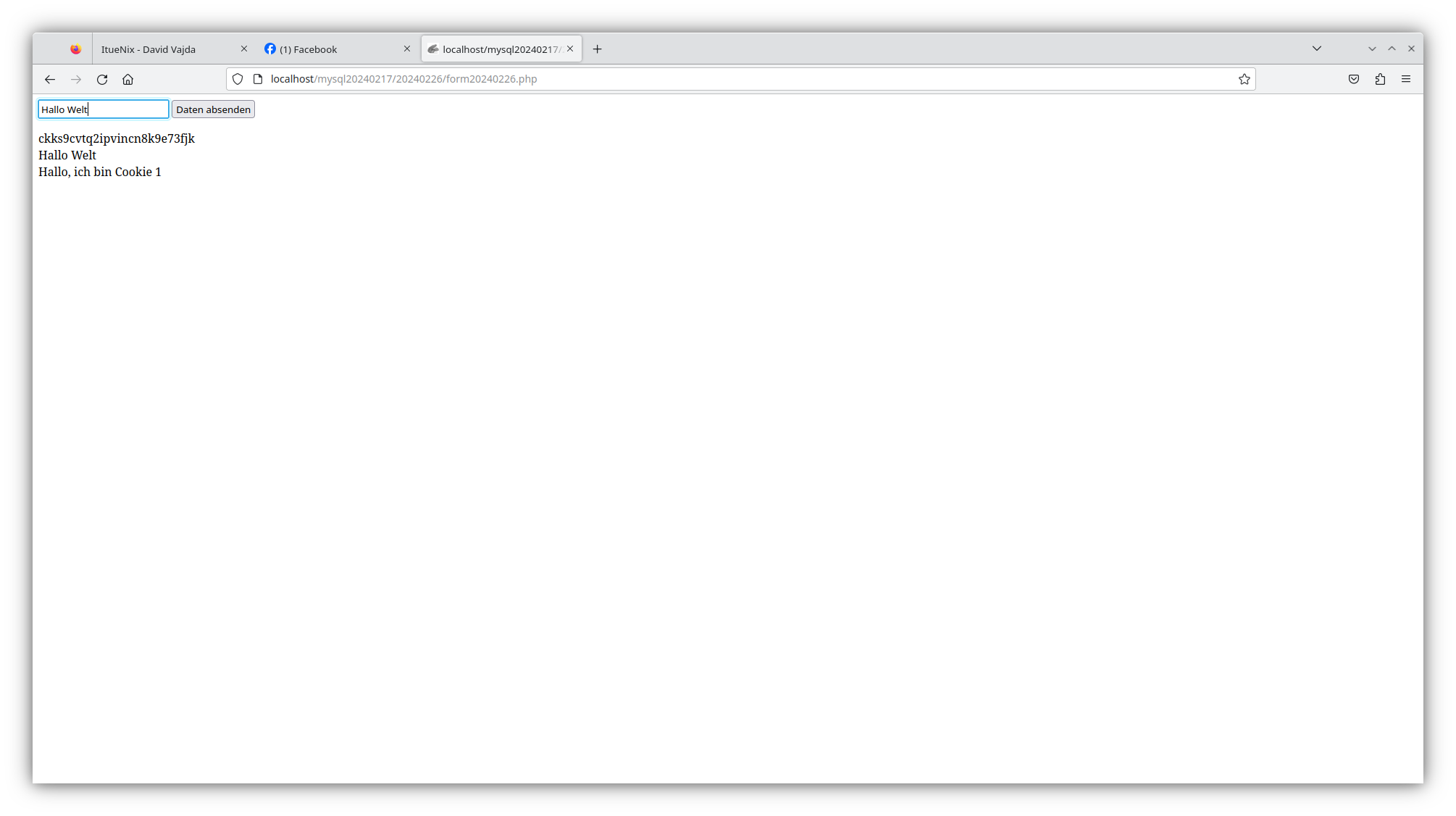

<?php

session_start ();

?>

<form method="POST" action="./form20240226.php">

<input type="text" name="2024022601"></input>

<input type="submit">

</form>

<?php

echo session_id () . "<br>n";

setcookie ("2024022602", "Hallo, ich bin Cookie 1", time () + 3600);

echo htmlentities (\$_POST ["2024022601"]) . "<br>n";

echo htmlentities (\$_COOKIE ["2024022602"]) . "<br>n";

echo htmlentities (\$_COOKIE ["2024022603"]) . "<br>n";

session_destroy ();

?>

POST http://localhost/mysql20240217/20240226/form20240226.php HTTP/1.1 host: localhost Cookie: 2024022603=Hallo, ich bin Cookie 2 Content-Length: 33 Content-Type: application/x-www-form-urlencoded 2024022601=Hallo ich bin Inhalt 1

Trying ::1... Connected to localhost. Escape character is '\^]'. HTTP/1.1 200 OK Date: Mon, 26 Feb 2024 14:58:13 GMT Server: Apache/2.4.57 (Debian) Set-Cookie: PHPSESSID=1cjt31i1h840f66hjh9h37qgch; path=/ Expires: Thu, 19 Nov 1981 08:52:00 GMT Cache-Control: no-store, no-cache, must-revalidate Pragma: no-cache Set-Cookie: 2024022602=Hallo%2C%20ich%20bin%20Cookie%201; expires=Mon, 26 Feb 2024 15:58:13 GMT; Max-Age=3600 Vary: Accept-Encoding Content-Length: 218 Content-Type: text/html; charset=UTF-8 <form method="POST" action="./form20240226.php"> <input type="text" name="2024022601"></input> <input type="submit"> </form> 1cjt31i1h840f66hjh9h37qgch<br> Hallo ich bin Inhalt 1<br> <br> Hallo, ich bin Cookie 2<br>

<?php

session_start ();

include ("/home/david/mysqldata.php");

\$db = new PDO ("mysql: host=localhost", \$MYSQL_USER, \$MYSQL_PASSWORD);

\$sql = "CREATE DATABASE mysql20240226" . session_id ();

\$db->query (\$sql);

\$sql = "USE mysql20240226" . session_id ();

\$db->query (\$sql);

\$sql = "CREATE TABLE a (x INTEGER);";

\$db->query (\$sql);

\$sql = "CREATE TABLE b (x INTEGER);";

\$db->query (\$sql);

\$sql = "CREATE TABLE c (x INTEGER);";

\$db->query (\$sql);

for (\$i = 0; \$i < 24; \$i++) {

\$sql = "INSERT INTO a (x) VALUES ("" . rand () % 32 . "")";

\$db->query (\$sql);

\$sql = "INSERT INTO b (x) VALUES ("" . rand () % 64 . "")";

\$db->query (\$sql);

\$sql = "INSERT INTO c (x) VALUES ("" . rand () % 28 . "")";

\$db->query (\$sql);

}

\$sql = "SELECT x FROM (SELECT x FROM a UNION SELECT x FROM b) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (SELECT x FROM a UNION SELECT x FROM c) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (SELECT x FROM b UNION SELECT x FROM c) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (SELECT x FROM a INTERSECT SELECT x FROM b) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (SELECT x FROM a INTERSECT SELECT x FROM c) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (SELECT x FROM b INTERSECT SELECT x FROM c) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (

SELECT x FROM (SELECT x FROM a UNION SELECT x FROM b) x

INTERSECT

SELECT x FROM c

) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (

SELECT x FROM (SELECT x FROM a INTERSECT SELECT x FROM c) x

UNION

SELECT x FROM (SELECT x FROM b INTERSECT SELECT x FROM c) x

) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (

SELECT x FROM (SELECT x FROM a UNION SELECT x FROM c) x

INTERSECT

SELECT x FROM b

) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (

SELECT x FROM (SELECT x FROM a INTERSECT SELECT x FROM b) x

UNION

SELECT x FROM (SELECT x FROM c INTERSECT SELECT x FROM b) x

) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (

SELECT x FROM (SELECT x FROM b UNION SELECT x FROM c) x

INTERSECT

SELECT x FROM a

) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "SELECT x FROM (

SELECT x FROM (SELECT x FROM b INTERSECT SELECT x FROM a) x

UNION

SELECT x FROM (SELECT x FROM c INTERSECT SELECT x FROM a) x

) x;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", ";

echo "<br>n";

\$sql = "DROP DATABASE mysql20240226" . session_id ();

\$db->query (\$sql);

session_destroy ();

?>

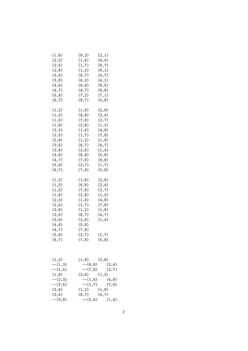

4, 30, 23, 27, 6, 25, 1, 19, 11, 13, 10, 8, 16, 7, 31, 35, 56, 55, 21, 57, 52, 22, 51, 44, 53, 32, 20, 49, 34, 47, 18, 41, <br> 4, 30, 23, 27, 6, 25, 1, 19, 11, 13, 10, 8, 16, 7, 31, 2, 3, 14, 20, 18, 9, 0, 15, 5, <br> 35, 56, 1, 4, 8, 55, 21, 57, 52, 22, 51, 44, 53, 32, 10, 20, 49, 34, 47, 18, 41, 2, 3, 14, 9, 0, 27, 13, 23, 15, 16, 5, <br> 4, 1, 10, 8, <br> 23, 27, 1, 13, 8, 16, <br> 1, 8, 20, 18, <br> 23, 27, 1, 13, 8, 16, 20, 18, <br> 23, 27, 1, 13, 8, 16, 20, 18, <br> 4, 1, 10, 8, 20, 18, <br> 4, 1, 10, 8, 20, 18, <br> 1, 4, 8, 10, 27, 13, 23, 16, <br> 1, 4, 8, 10, 27, 13, 23, 16, <br>

<?php

session_start ();

include ("/home/david/mysqldata.php");

\$db = new PDO ("mysql: host=localhost", \$MYSQL_USER, \$MYSQL_PASSWORD);

\$sql = "CREATE DATABASE mysql20240226b" . session_id ();

\$db->query (\$sql);

\$sql = "USE mysql20240226b" . session_id ();

\$db->query (\$sql);

\$sql = "CREATE TABLE a (x1 INTEGER, x2 INTEGER);";

\$db->query (\$sql);

\$sql = "CREATE TABLE b (y1 INTEGER, y2 INTEGER);";

\$db->query (\$sql);

\$sql = "INSERT INTO a (x1, x2) VALUES (0, 0);";

\$db->query (\$sql);

\$sql = "INSERT INTO a (x1, x2) VALUES (0, 1);";

\$db->query (\$sql);

\$sql = "INSERT INTO a (x1, x2) VALUES (1, 0);";

\$db->query (\$sql);

\$sql = "INSERT INTO a (x1, x2) VALUES (1, 1);";

\$db->query (\$sql);

\$sql = "INSERT INTO a (x1, x2) VALUES (2, 7);";

\$db->query (\$sql);

\$sql = "INSERT INTO b (y1, y2) VALUES (0, 1);";

\$db->query (\$sql);

\$sql = "INSERT INTO b (y1, y2) VALUES (1, 0);";

\$db->query (\$sql);

\$sql = "INSERT INTO b (y1, y2) VALUES (2, 7);";

\$db->query (\$sql);

\$sql = "SELECT x1, x2 FROM a;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", " . \$row [1] . "<br>n";

echo "<br>n";

\$sql = "SELECT y1, y2 FROM b;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", " . \$row [1] . "<br>n";

echo "<br>n";

\$sql = "SELECT x1, x2, y1, y2 FROM a INNER JOIN b;";

\$stmt = \$db->query (\$sql);

while (\$row = \$stmt -> fetch ())

echo \$row [0] . ", " . \$row [1] . ", " . \$row [2] . ", " . \$row [3] . "<br>n";

echo "<br>n";

\$sql = "DROP DATABASE mysql20240226b" . session_id ();

\$db->query (\$sql);

session_destroy ();

?>

0, 0<br> 0, 1<br> 1, 0<br> 1, 1<br> 2, 7<br> <br> 0, 1<br> 1, 0<br> 2, 7<br> <br> 0, 0, 0, 1<br> 0, 0, 1, 0<br> 0, 0, 2, 7<br> 0, 1, 0, 1<br> 0, 1, 1, 0<br> 0, 1, 2, 7<br> 1, 0, 0, 1<br> 1, 0, 1, 0<br> 1, 0, 2, 7<br> 1, 1, 0, 1<br> 1, 1, 1, 0<br> 1, 1, 2, 7<br> 2, 7, 0, 1<br> 2, 7, 1, 0<br> 2, 7, 2, 7<br> <br>

So, ich mache jetzt noch die üblichen Bash Übungen. Dann mache ich noch schriftliche Multiplikation und Division. Danach gehe ich noch mal auf die Platanenallee. Und danach mache ich die üblichen Übungen zu

1.) VHDL und Quine Mc Cluskey 2.) Zuständen 3.) ASM-Diagramm 4.) IEEE754 5.) Aber auch Assembler Programme. Ich schreibe in MIPS 32 Assembler

#!/bin/bash echo "Hallo Welt"

Hallo Welt

#!/bin/bash

i=0

while [ \$i -lt 10 ]

do

echo "Hallo zum \$((\$i+1))."

i=\$((\$i+1))

done

Hallo zum 1. Hallo zum 2. Hallo zum 3. Hallo zum 4. Hallo zum 5. Hallo zum 6. Hallo zum 7. Hallo zum 8. Hallo zum 9. Hallo zum 10.

#!/bin/bash

if [[ "\$1" == "David" \&\& "\$2" == "Vajda" ]]

then

echo "Das bin ich"

elif [ "\$1" == "David Vajda" ]

then

echo "Das bin ich"

elif [ "\$1" == "David" ]

then

echo "Das bin wahrscheinlich ich"

elif [ "\$1" == "Vajda" ]

then

echo "Das bin wahrscheinlich ich"

else

echo "Das bin ich nicht"

fi

#!/bin/bash /bin/bash ifthenelse.sh "David" "Vajda" >> ifthenelse.out /bin/bash ifthenelse.sh "David Vajda" >> ifthenelse.out /bin/bash ifthenelse.sh "David" >> ifthenelse.out /bin/bash ifthenelse.sh "Vajda" >> ifthenelse.out /bin/bash ifthenelse.sh "Max Mustermann" >> ifthenelse.out

Das bin ich Das bin ich Das bin wahrscheinlich ich Das bin wahrscheinlich ich Das bin ich nicht

#!/bin/bash

a=(Hallo dies ist ein Array)

a+=(Und das eine Erweiterung)

i=0

while [ \$i -lt 9 ]

do

echo "\${a[\$i]}"

i=\$((\$i+1))

done

for s in "\${a[@]}"

do

echo "\$s"

done

Hallo dies ist ein Array Und das eine Erweiterung Hallo dies ist ein Array Und das eine Erweiterung

#!/bin/bash

l=\$(ls)

for s in \$l

do

echo "\$s"

done

array.out array.sh cmd.out cmd.sh hello.out hello.sh ifthenelsecmd.sh ifthenelse.out ifthenelse.sh while.out while.sh

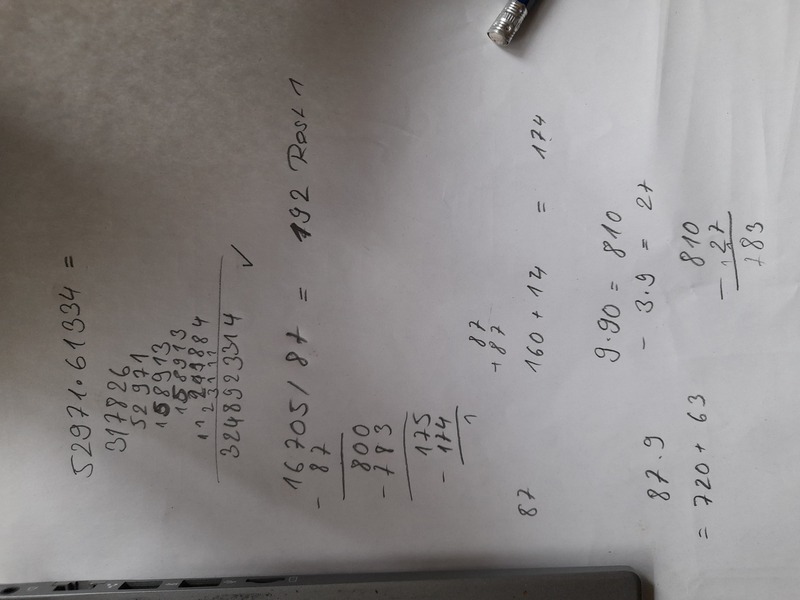

So, jetzt kommt das von Hand rechnen. Einen Moment, danach kurz auf die Allee.

1.) Rechne die Zahl in binaer Darstellung in eine Dezimale Darstellung um

1011111100011011b 48923d

2.) Rechne die Zahl in dezimal darstellung in eine Binaerdarstellung um

42107 1010010001111011

3.) Addiere die drei Zahlen schriftlich

58823

+ 5867

+ 49359

-----------------

114049

4.) Subtrahiere die letzten drei Zahlen schriftlich von der ersten schriftlich

21416

- 271

- 10576

- 4657

-----------------

5912

5.) Rechne die Zahl ins zweier komplement um, mit 8 Bit - und subtrahiere diese zahl von der ersten und rechne das Ergebnis nach dezimal

-87 -103 = -190

10101001 10011001 = 01000010

6.) Multipliziere die zwei Zahlen schriftlich

52971*61334 = 3248923314

7.) Dividiere die zwei Zahlen schriftlich

876/16705 = 0

8.) Errechne x Logarithmisch mit dem Taschenrechner

29737\^x = 530920564

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 1

5 0 1 0 1 0

6 0 1 1 0 1

7 0 1 1 1 0

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 0

11 1 0 1 1 0

12 1 1 0 0 0

13 1 1 0 1 0

14 1 1 1 0 1

15 1 1 1 1 0

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

4 0 1 0 0 1

6 0 1 1 0 1

8 1 0 0 0 1

14 1 1 1 0 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

4 0 1 0 0 1

8 1 0 0 0 1

Gruppe 2:

6 0 1 1 0 1

Gruppe 3:

14 1 1 1 0 1

0:1 0 0 0 -

0:2 0 0 - 0

0:4 0 - 0 0

0:8 - 0 0 0

2:6 0 - 1 0

4:6 0 1 - 0

6:14 - 1 1 0

0:1 0 0 0 -

0:2 0 0 - 0

4:6 0 1 - 0

0:4 0 - 0 0

2:6 0 - 1 0

0:8 - 0 0 0

6:14 - 1 1 0

Gruppe 0:

0:1 0 0 0 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

4:6 0 1 - 0

Gruppe 0:

0:4 0 - 0 0

Gruppe 1:

2:6 0 - 1 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 2:

6:14 - 1 1 0

Gruppe 0:

0:1 0 0 0 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

4:6 0 1 - 0

0:2:4:6 0 - - 0

Gruppe 0:

0:4 0 - 0 0

Gruppe 1:

2:6 0 - 1 0

0:4:2:6 0 - - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 2:

6:14 - 1 1 0

0:1 0 0 0 -

0:2:4:6 0 - - 0

0:4:2:6 0 - - 0

0:8 - 0 0 0

6:14 - 1 1 0

0:1 0 0 0 -

0:2:4:6 0 - - 0

0:8 - 0 0 0

6:14 - 1 1 0

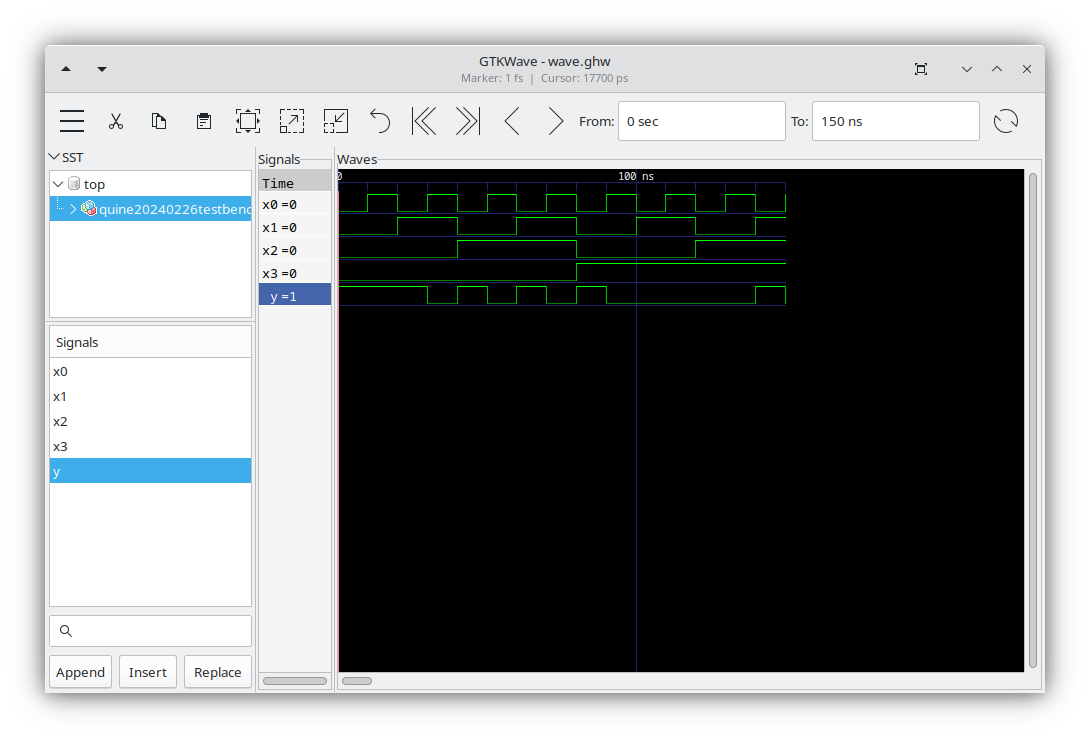

y <= (not x3 and not x2 and not x1) or

(not x3 and not x0) or

(not x2 and not x1 and not x0) or

(x2 and x1 and not x0);

y <= not (

(x3 or x2 or x1) and

(x3 or x0) and

(x2 or x1 or x0) and

(not x2 or not x1 or x0)

);

library ieee;

use ieee.std_logic_1164.all;

entity quine20240226 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture behaviour of quine20240226 is

begin

y <= (not x3 and not x2 and not x1) or

(not x3 and not x0) or

(not x2 and not x1 and not x0) or

(x2 and x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240226testbench is

port (

y: out std_logic

);

end;

architecture behaviour of quine20240226testbench is

component quine20240226

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

q: quine20240226 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

library ieee;

use ieee.std_logic_1164.all;

entity quine20240226 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end;

architecture behaviour of quine20240226 is

begin

y <= (not x3 and not x2 and not x1) or

(not x3 and not x0) or

(not x2 and not x1 and not x0) or

(x2 and x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity quine20240226testbench is

port (

y: out std_logic

);

end;

architecture behaviour of quine20240226testbench is

component quine20240226

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0: std_logic;

begin

q: quine20240226 PORT MAP (x3=>x3, x2=>x2, x1=>x1, x0=>x0, y=>y);

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x2 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '0' after 100 ns, '0' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

x3 <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '0' after 40 ns, '0' after 50 ns, '0' after 60 ns, '0' after 70 ns, '1' after 80 ns, '1' after 90 ns, '1' after 100 ns, '1' after 110 ns, '1' after 120 ns, '1' after 130 ns, '1' after 140 ns, '1' after 150 ns;

end;

Jetzt eine IEEE-754-Umrechung - dann nachher zu Hause weiter.

12.78125 12/2 = 6 Rest 0 6/2 = 3 Rest 0 3/2 = 1 Rest 1 1/2 = 1 Rest 1 0.78125 * 2 = 1.56250 1 0.56250 * 2 = 1.12500 1 0.12500 * 2 = 0.25 0 0.25 * 2 = 0.5 0 0.5 * 2 = 1.0 1 0.78125 0.78125 ------- 1.56250 0.56250 0.56250 ------- 1.12500 1100,11001 1100,11001 = 1,10011001 * 2\^3 normalisiert: 10011001 127 + 3 = 130 130 / 2 = 65 Rest 0 65 / 2 = 32 Rest 1 32 / 2 = 16 Rest 0 16 / 2 8 Rest 0 8 / 2 = 4 Rest 0 4 / 2 = 2 Rest 0 2 / 2 = 1 Rest 0 1 / 2 = 0 Rest 1 [0][10000010][10011001] 0100.0001.0100.1100.1 0100.0001.0100.1100.1000.0000.0000 0x414C800

Nur, um es nebenbei zu sagen, kann ich mit LaTeX schöne Zustände machen. Sage ich für Facebook

Sie müssen mein Programm jetzt erst verstehen, ich hatte das ja vorgestellt. Aber sie wissen ja, wie die Faker so sind, kaum hat man das auf Facebook verschwinden lassen, tun sie so als hätten sie es nicht gehört

Also, der Witz ist - eigentlich tut das Programm folgendes, das generiert zum beispiel so eine Datei. VCS

Zustand,Eingabe,Ausgabe,Folgezustand 1,0,0,3 1,1,1,4 2,0,1,1 2,1,0,1 3,0,1,4 3,1,1,3 4,0,1,2 4,1,1,2

Der Unterschied ist halt - das Programm kann auch direkt PDF generieren. Es kann neue Daten erzeugen, sie ausgeben, oder einlesen. Von einer Tabelle.

Der Unterschied zwischen VCS und PDF ist, oder TeX. Das macht ja ein *.tex document. dass das Tex nicht verarbeitet werden kann, nicht gut. Die tabelle halt in VCS

Das könnte auch in eine Datenbank

Egal. VCS ist normal, Tabelle. da sind die Zustände drin. normalerweise erst das generieren, dann daraus ein Tex Ding. Dann mit LaTeX übersetzen. Das geht so:

david@laptop-peaq:~\$ ./automat15 Zustand,Eingabe,Ausgabe,Folgezustand 1,0,0,1 1,1,0,2 2,0,1,2 2,1,0,4 3,0,1,3 3,1,1,1 4,0,0,4 4,1,1,3 david@laptop-peaq:~\$ ./automat15 > automat20240226.vcs david@laptop-peaq:~\$ cat automat20240226.vcs | ./automat15 -s -t >> automat20240226.tex david@laptop-peaq:~\$ pdflatex automat20240226.tex

So, OK. Und der Witz ist - dass sie dann das PDF haben. Und da ist jetzt alles automatisch generiert. Das heisst, der Graph von den zuständen, dann die Zustandstabelle aber auch. Und dann auch noch die Gleichungen

Das Ziel ist ja die Übung, das heisst, man macht nur den Graph. Dafür manipuliert man das TeX ding. Das ist nur zur Kontrolle. Man nimmt halt alles aus dem Graph raus. Speichert es ist einer zweiten Datei. Und guckt den Graph an und macht die Gleichung die Tabelle selber

Und für alle Faker. Ja, da war ein Fehler im Programm. der hat bei den Gleichungen, die NOT vertauscht. Egal. Der Fehler ist schnell behoben, das war die zeit als ich auf die Prüfung lernte.

gut. Dann fange ich jetzt an. Mit der Übung. Selber.

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= not d;

r1 <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

c <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns,

'0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns,

'1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d <= '0' after 0 ns, '1' after 150 ns, '0' after 250 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

we: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

dmsflipflop1: dmsflipflop PORT MAP (q=>q(i), d=>d(i), c=>we);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32testbench is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal we: std_logic;

begin

reg32a: reg32 PORT MAP (d=>d, q=>q, we=>we);

d(0) <= '1';

d(1) <= '0';

d(2) <= '1';

d(3) <= '0';

d(4) <= '1';

d(5) <= '0';

d(6) <= '1';

d(7) <= '0';

d(8) <= '1';

d(9) <= '1';

d(10) <= '0';

d(11) <= '1';

d(12) <= '0';

d(13) <= '1';

d(14) <= '0';

d(15) <= '1';

d(16) <= '0';

d(17) <= '1';

d(18) <= '0';

d(19) <= '1';

d(20) <= '0';

d(21) <= '1';

d(22) <= '0';

d(23) <= '1';

d(24) <= '0';

d(25) <= '1';

d(26) <= '0';

d(27) <= '1';

d(28) <= '0';

d(29) <= '1';

d(30) <= '0';

d(31) <= '1';

we <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32 is

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32 is

begin

-- 00000

b (0) <= not a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 00001

b (1) <= not a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 00010

b (2) <= not a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 00011

b (3) <= not a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 00100

b (4) <= not a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 00101

b (5) <= not a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 00110

b (6) <= not a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 00111

b (7) <= not a (4) and not a (3) and a (2) and a (1) and a (0);

-- 01000

b (8) <= not a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 01001

b (9) <= not a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 01010

b (10) <= not a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 01011

b (11) <= not a (4) and a (3) and not a (2) and a (1) and a (0);

-- 01100

b (12) <= not a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 01101

b (13) <= not a (4) and a (3) and a (2) and not a (1) and a (0);

-- 01110

b (14) <= not a (4) and a (3) and a (2) and a (1) and not a (0);

-- 01111

b (15) <= not a (4) and a (3) and a (2) and a (1) and a (0);

-- 10000

b (16) <= a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 10001

b (17) <= a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 10010

b (18) <= a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 10011

b (19) <= a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 10100

b (20) <= a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 10101

b (21) <= a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 10110

b (22) <= a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 10111

b (23) <= a (4) and not a (3) and a (2) and a (1) and a (0);

-- 11000

b (24) <= a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 11001

b (25) <= a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 11010

b (26) <= a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 11011

b (27) <= a (4) and a (3) and not a (2) and a (1) and a (0);

-- 11100

b (28) <= a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 11101

b (29) <= a (4) and a (3) and a (2) and not a (1) and a (0);

-- 11110

b (30) <= a (4) and a (3) and a (2) and a (1) and not a (0);

-- 11111

b (31) <= a (4) and a (3) and a (2) and a (1) and a (0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32testbench is

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (4 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (b=>q, a=>d);

d (0) <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns, '1' after 170 ns, '0' after 180 ns, '1' after 190 ns, '0' after 200 ns, '1' after 210 ns, '0' after 220 ns, '1' after 230 ns, '0' after 240 ns, '1' after 250 ns, '0' after 260 ns, '1' after 270 ns, '0' after 280 ns, '1' after 290 ns, '0' after 300 ns, '1' after 310 ns;

d (1) <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns, '0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns, '1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d (2) <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns, '1' after 120 ns, '0' after 160 ns, '1' after 200 ns, '0' after 240 ns, '1' after 280 ns, '0' after 320 ns, '1' after 360 ns;

d (3) <= '0' after 0 ns, '1' after 80 ns, '0' after 160 ns, '1' after 240 ns, '0' after 320 ns, '1' after 400 ns;

d (4) <= '0' after 0 ns, '1' after 160 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset32x32 is

port (

writereg: in std_logic_vector (4 downto 0);

readreg1: in std_logic_vector (4 downto 0);

readreg2: in std_logic_vector (4 downto 0);

readport1: out std_logic_vector (31 downto 0);

readport2: out std_logic_vector (31 downto 0);

writeport: in std_logic_vector (31 downto 0);

we: in std_logic

);

end;

architecture behaviour of registerset32x32 is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal writereg1: std_logic_vector (31 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (a=>writereg, b=>writereg1);

l1:

for i in 0 to 31 generate

reg32a: reg32 PORT MAP (we=>writereg1(i),d=>writeport,q=>readport1); -- WARNING - WARNING

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

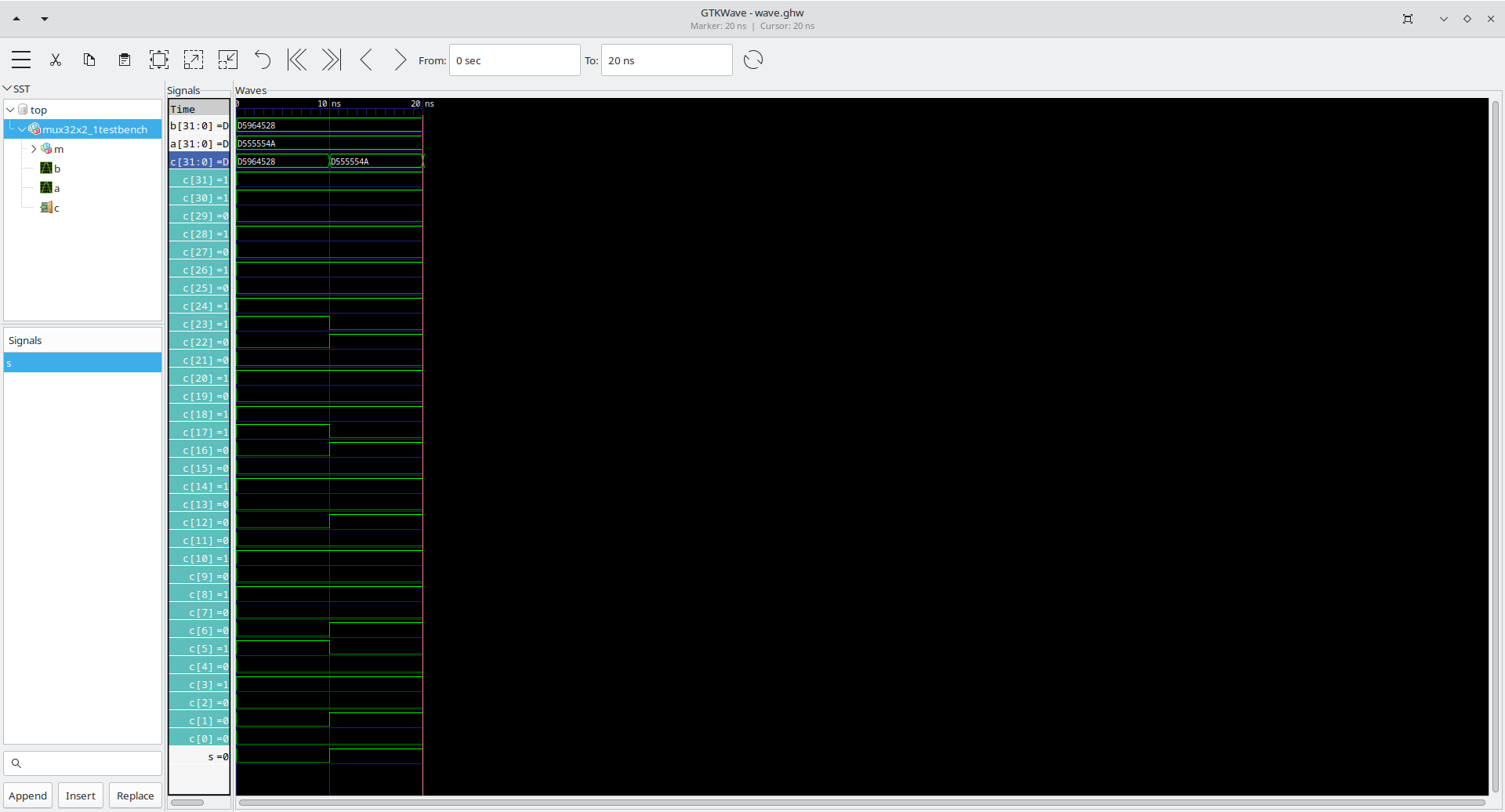

entity mux32x2_1 is

port (

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic

);

end;

architecture behaviour of mux32x2_1 is

begin

l1:

for i in 0 to 31 generate

c (i) <= (a (i) and s) or (b (i) and not s);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity mux32x2_1testbench is

port (

c: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of mux32x2_1testbench is

component mux32x2_1

port (

b: in std_logic_vector (31 downto 0);

a: in std_logic_vector (31 downto 0);

c: out std_logic_vector (31 downto 0);

s: in std_logic

);

end component;

signal a: std_logic_vector (31 downto 0);

signal b: std_logic_vector (31 downto 0);

signal s: std_logic;

begin

m: mux32x2_1 PORT MAP (b=>b, a=>a, c=>c, s=>s);

a (0) <= '0';

a (1) <= '1';

a (2) <= '0';

a (3) <= '1';

a (4) <= '0';

a (31) <= '1';

a (5) <= '0';

a (6) <= '1';

a (7) <= '0';

a (8) <= '1';

a (9) <= '0';

a (10) <= '1';

a (11) <= '0';

a (12) <= '1';

a (13) <= '0';

a (14) <= '1';

a (15) <= '0';

a (16) <= '1';

a (17) <= '0';

a (18) <= '1';

a (19) <= '0';

a (20) <= '1';

a (21) <= '0';

a (22) <= '1';

a (23) <= '0';

a (24) <= '1';

a (25) <= '0';

a (26) <= '1';

a (27) <= '0';

a (28) <= '1';

a (29) <= '0';

a (30) <= '1';

b (0) <= '0';

b (1) <= '0';

b (2) <= '0';

b (3) <= '1';

b (4) <= '0';

b (31) <= '1';

b (5) <= '1';

b (6) <= '0';

b (7) <= '0';

b (8) <= '1';

b (9) <= '0';

b (10) <= '1';

b (11) <= '0';

b (12) <= '0';

b (13) <= '0';

b (14) <= '1';

b (15) <= '0';

b (16) <= '0';

b (17) <= '1';

b (18) <= '1';

b (19) <= '0';

b (20) <= '1';

b (21) <= '0';

b (22) <= '0';

b (23) <= '1';

b (24) <= '1';

b (25) <= '0';

b (26) <= '1';

b (27) <= '0';

b (28) <= '1';

b (29) <= '0';

b (30) <= '1';

s <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns;

end;