Nächste Seite: Re: Das neue Auswendig Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Das neue Auswendig

-- https://phpbb3.ituenix.de/viewtopic.php?p=2504\&sid=fe31b12ff2b3b374eaca692913acc42d#p2504

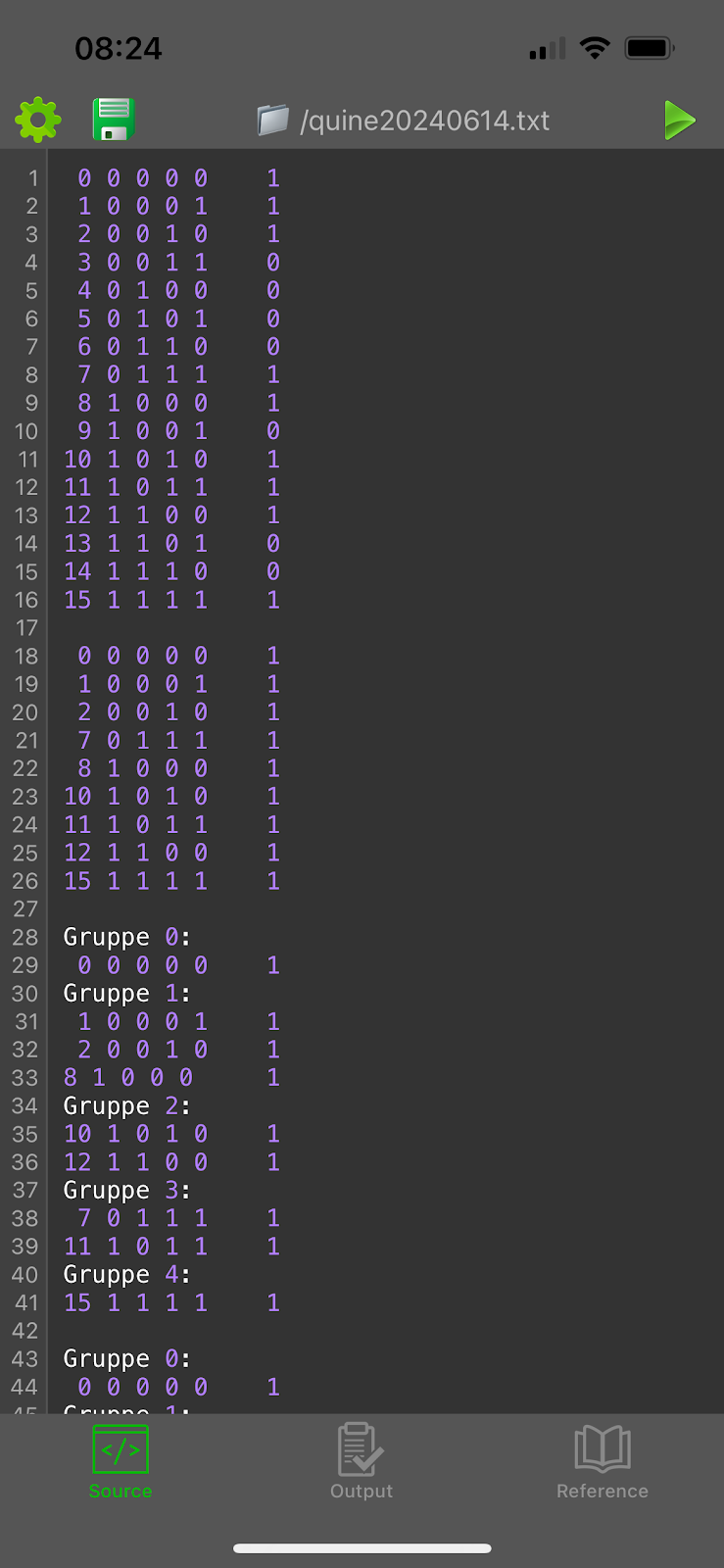

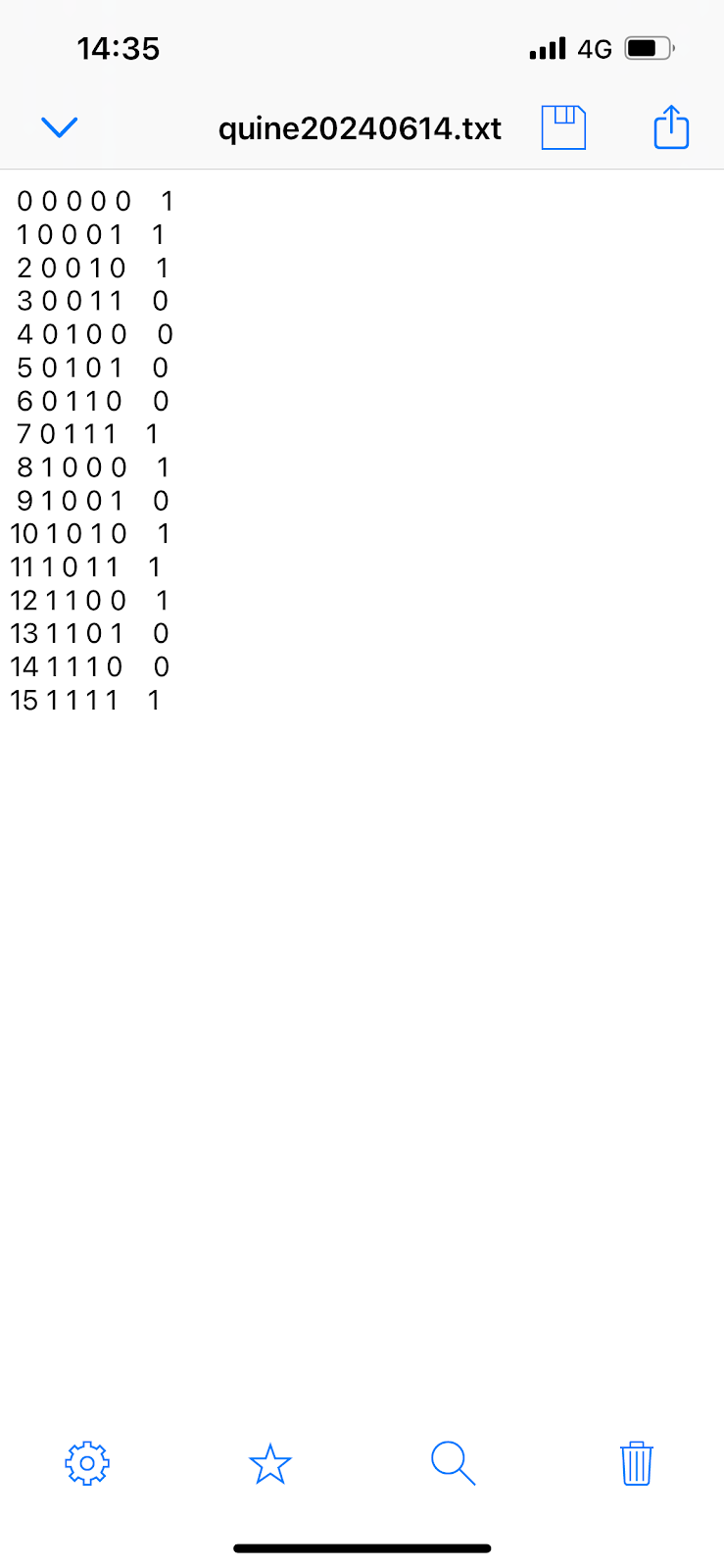

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

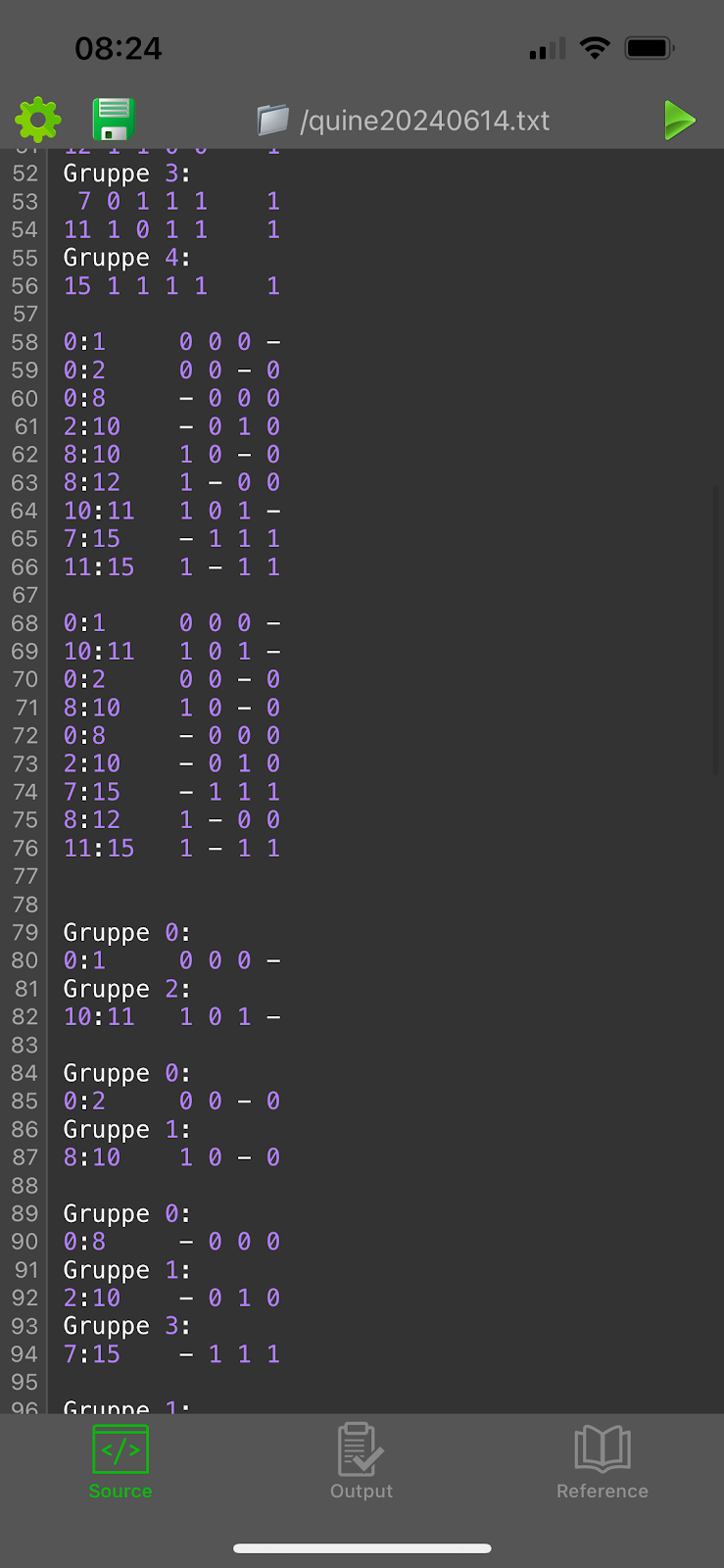

0:1 0 0 0 -

0:2 0 0 - 0

0:8 - 0 0 0

2:10 - 0 1 0

8:10 1 0 - 0

8:12 1 - 0 0

10:11 1 0 1 -

7:15 - 1 1 1

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

0:2 0 0 - 0

8:10 1 0 - 0

0:8 - 0 0 0

2:10 - 0 1 0

7:15 - 1 1 1

8:12 1 - 0 0

11:15 1 - 1 1

Gruppe 0:

0:1 0 0 0 -

Gruppe 2:

10:11 1 0 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

8:10 1 0 - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

2:10 - 0 1 0

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 3:

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

8:10 1 0 - 0

0:2:8:10 - 0 - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

2:10 - 0 1 0

0:8:2:10 - 0 - 0

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 3:

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

0:2:8:10 - 0 - 0

7:15 - 1 1 1

8:12 1 - 0 0

11:15 1 - 1 1

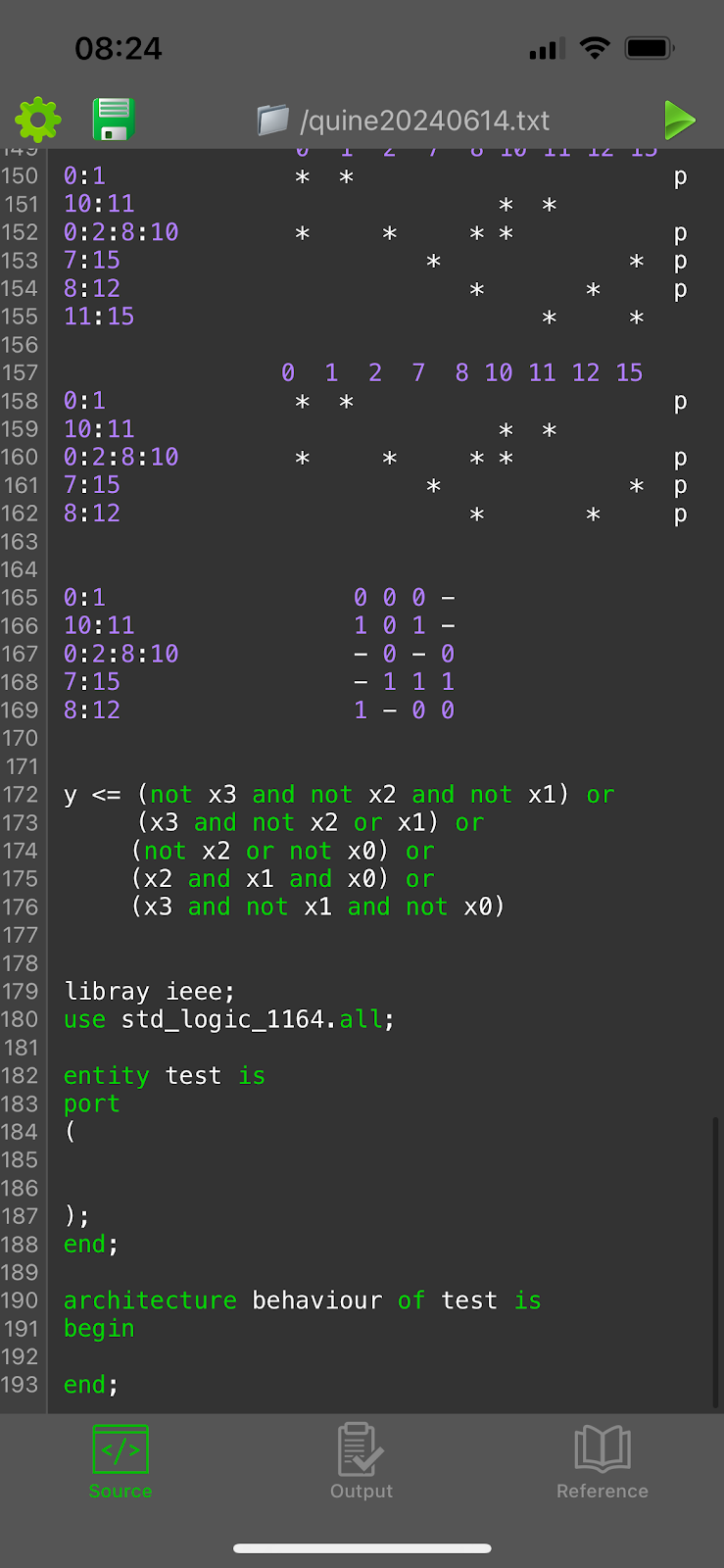

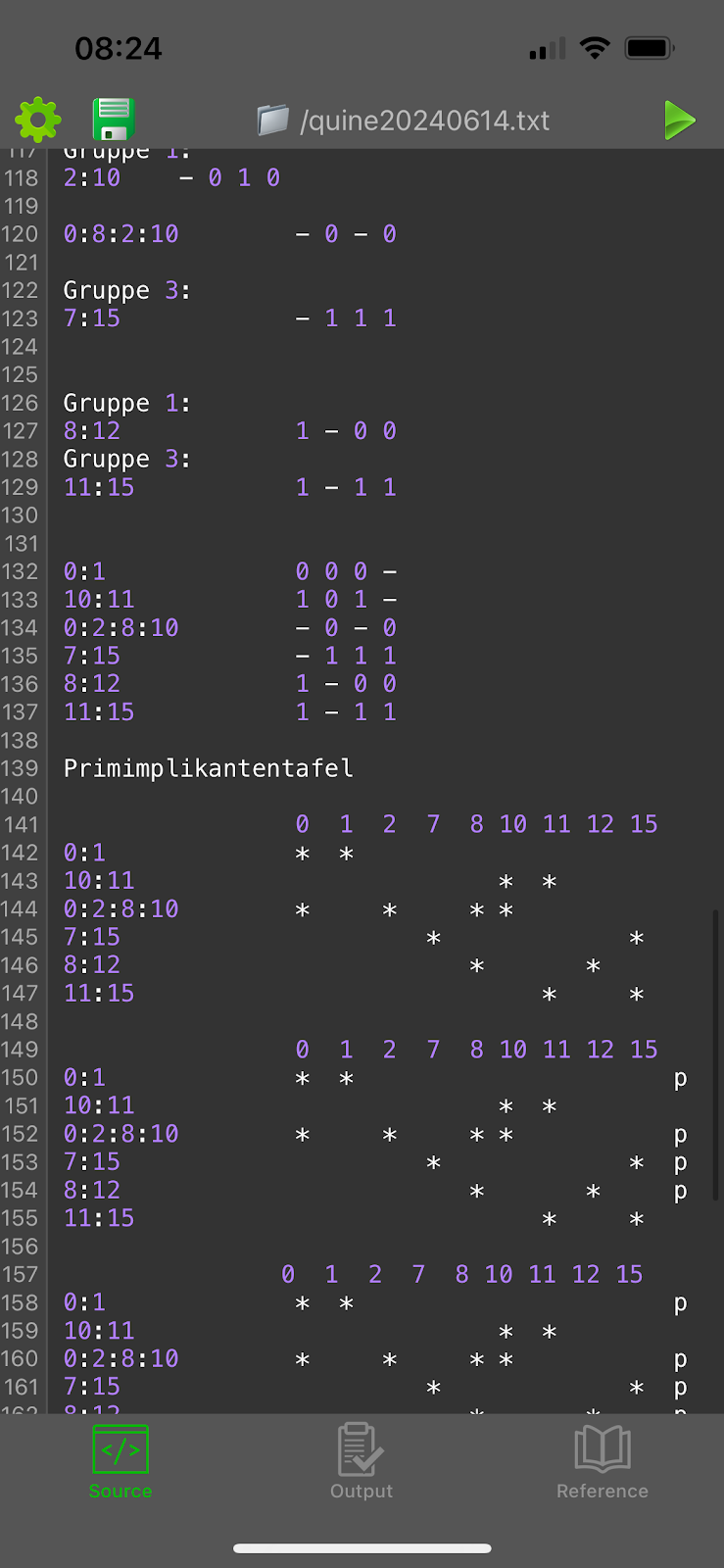

Primimplikantentafel

0 1 2 7 8 10 11 12 15

0:1 * *

10:11 * *

0:2:8:10 * * * *

7:15 * *

8:12 * *

11:15 * *

0 1 2 7 8 10 11 12 15

0:1 * * p

10:11 * *

0:2:8:10 * * * * p

7:15 * * p

8:12 * * p

11:15 * *

0 1 2 7 8 10 11 12 15

0:1 * * p

10:11 * *

0:2:8:10 * * * * p

7:15 * * p

8:12 * * p

0:1 0 0 0 -

10:11 1 0 1 -

0:2:8:10 - 0 - 0

7:15 - 1 1 1

8:12 1 - 0 0

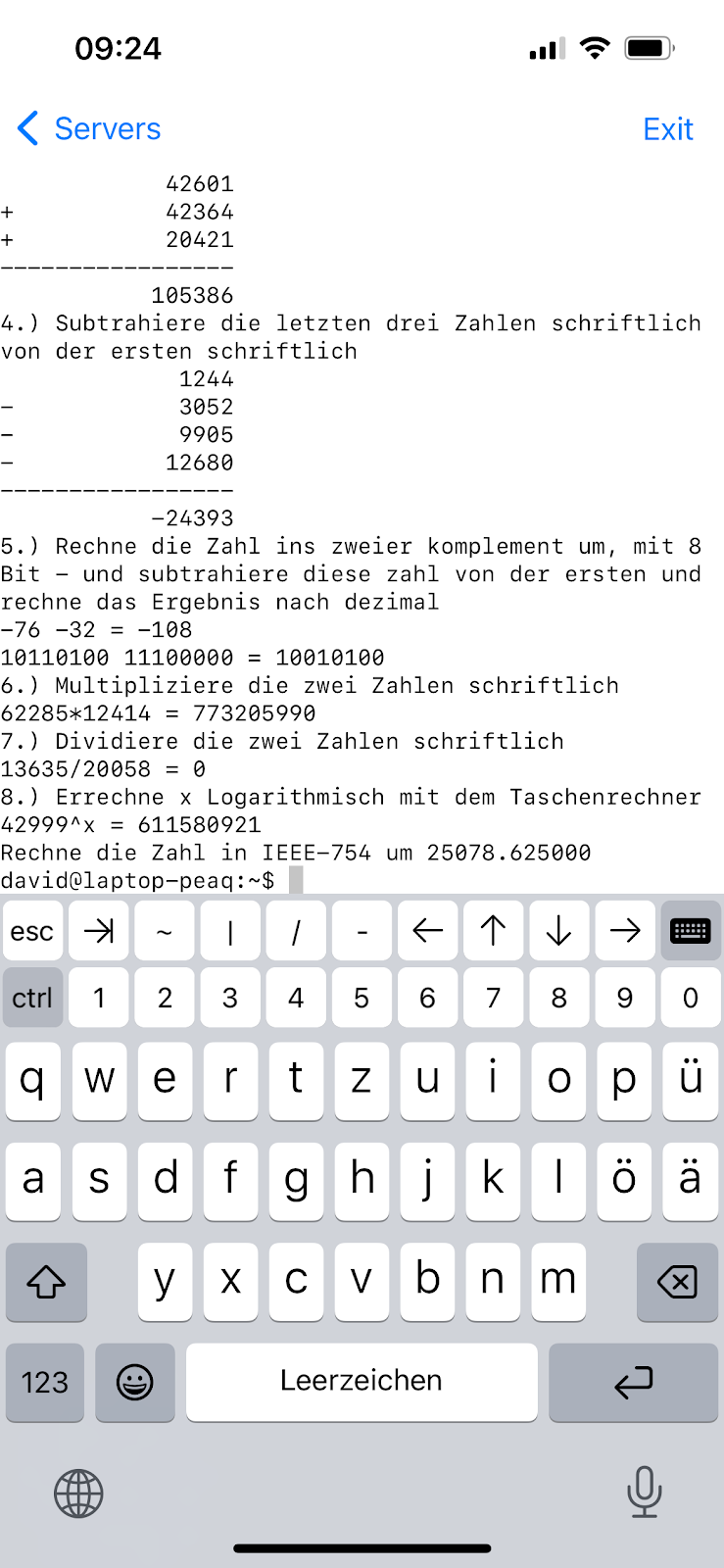

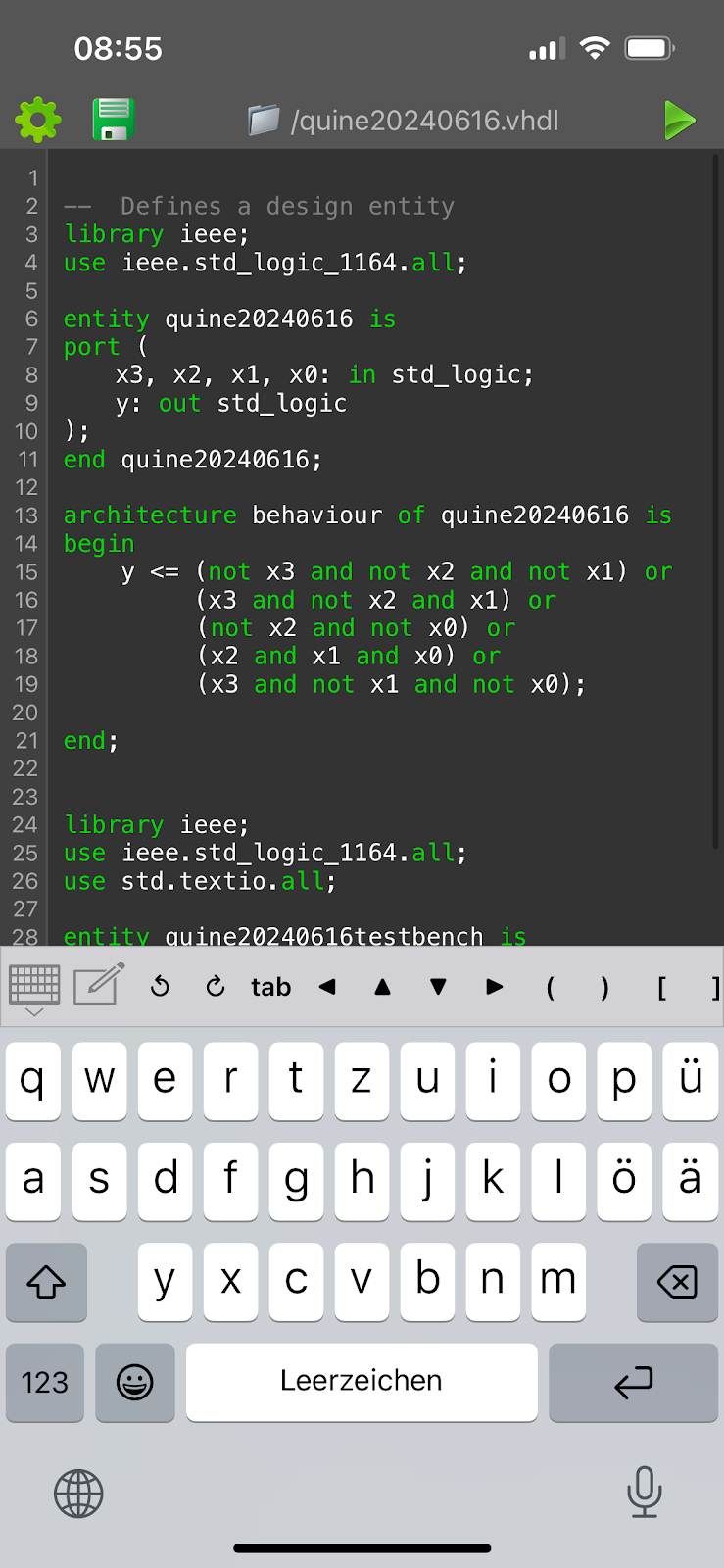

y <= (not x3 and not x2 and not x1) or

(x3 and not x2 or x1) or

(not x2 or not x0) or

(x2 and x1 and x0) or

(x3 and not x1 and not x0)

libray ieee;

use std_logic_1164.all;

entity test is

port

(

);

end;

architecture behaviour of test is

begin

end;

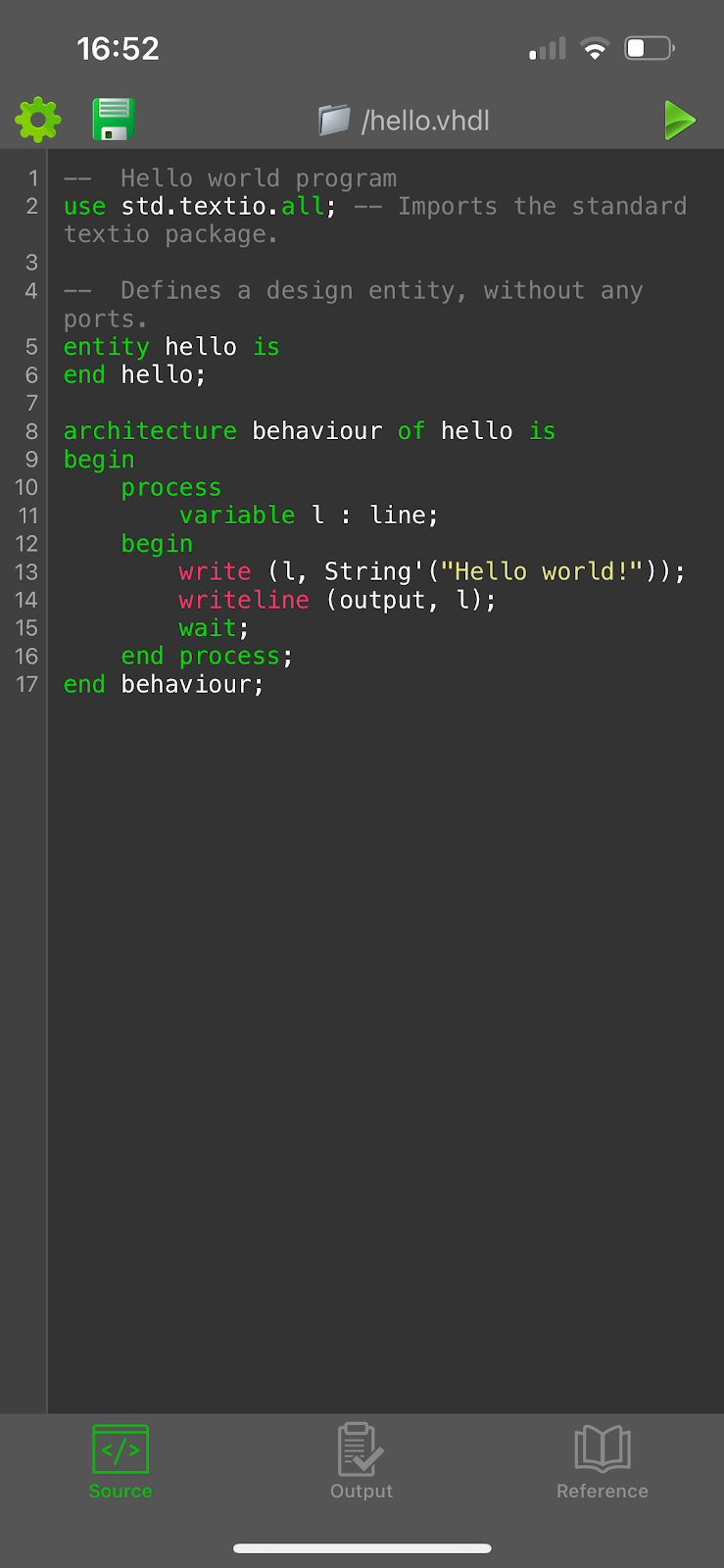

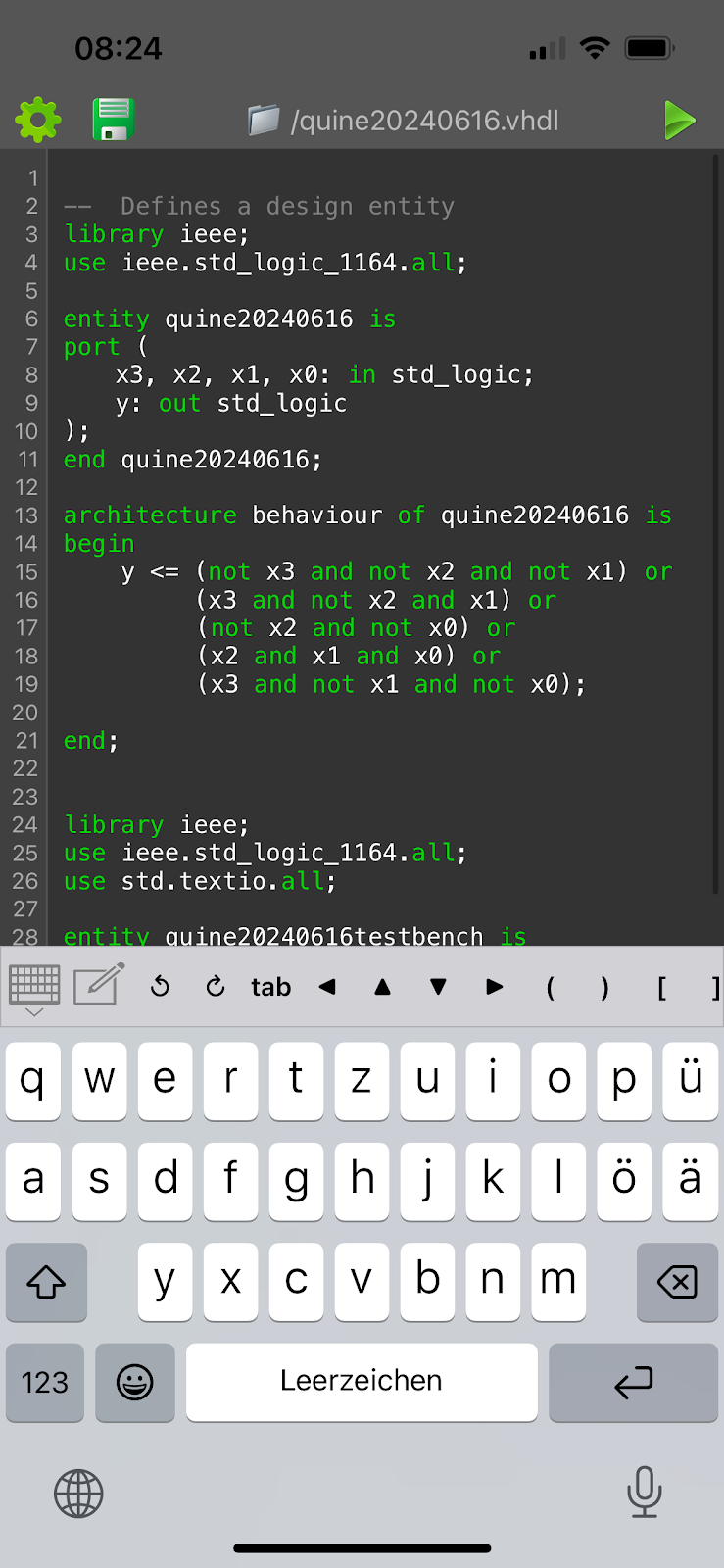

-- Defines a design entity

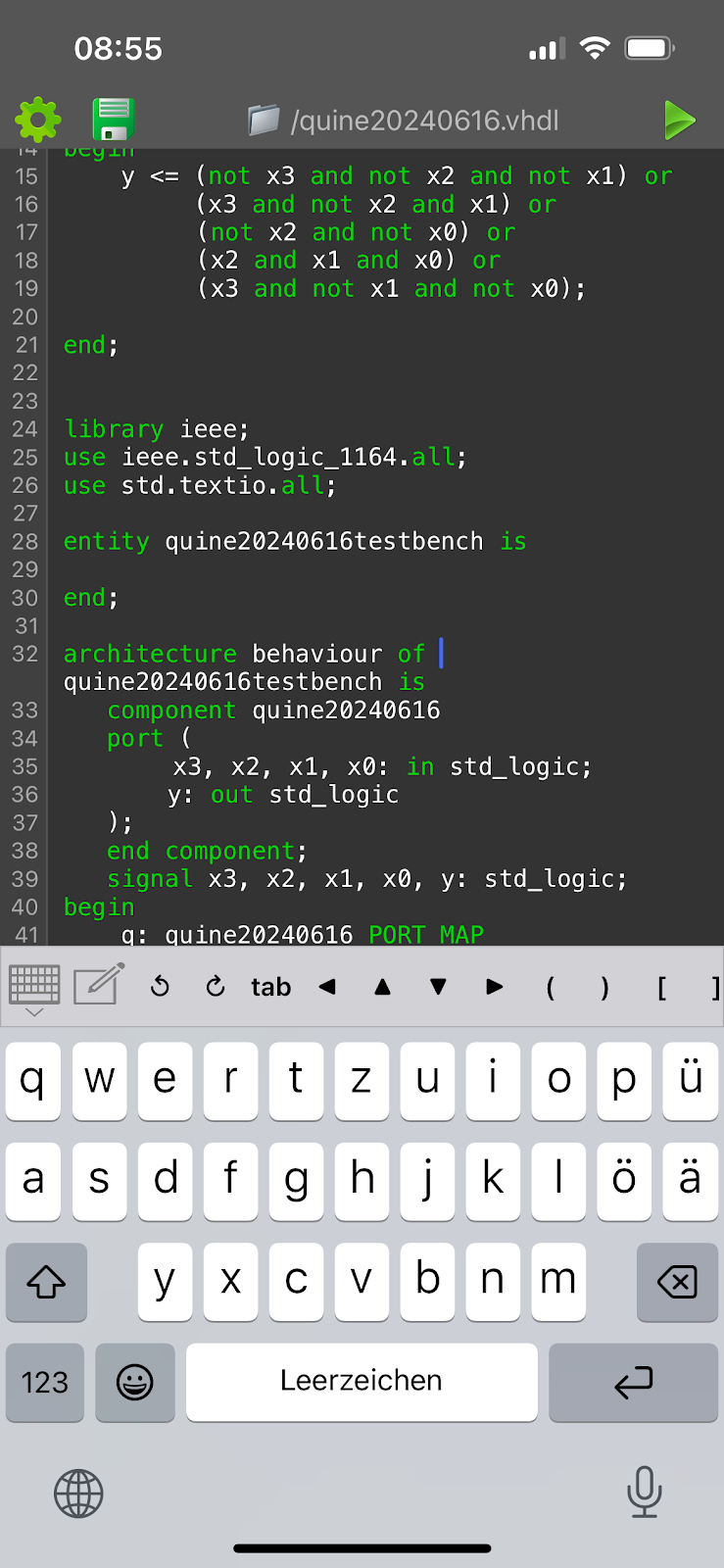

library ieee;

use ieee.std_logic_1164.all;

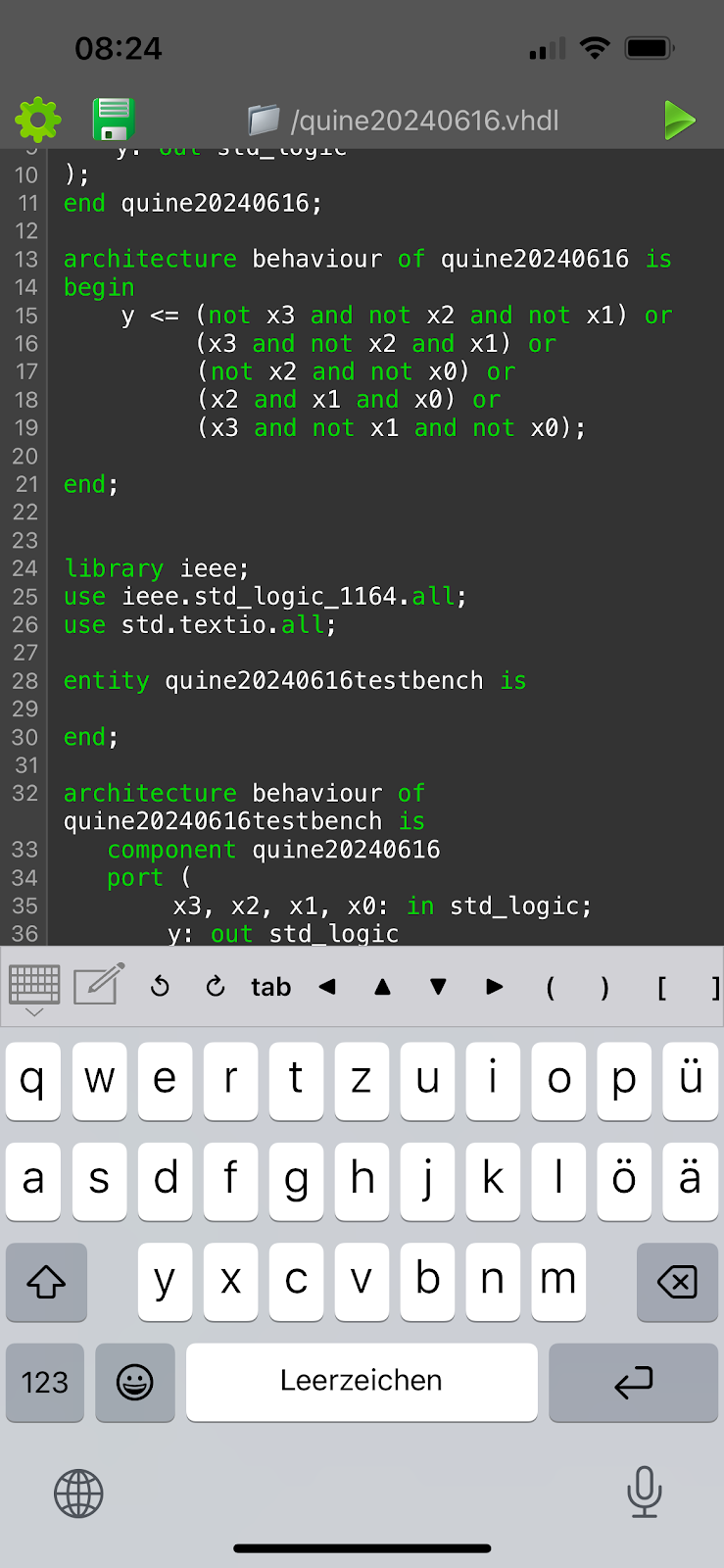

entity quine20240616 is

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end quine20240616;

architecture behaviour of quine20240616 is

begin

y <= (not x3 and not x2 and not x1) or

(x3 and not x2 and x1) or

(not x2 and not x0) or

(x2 and x1 and x0) or

(x3 and not x1 and not x0);

end;

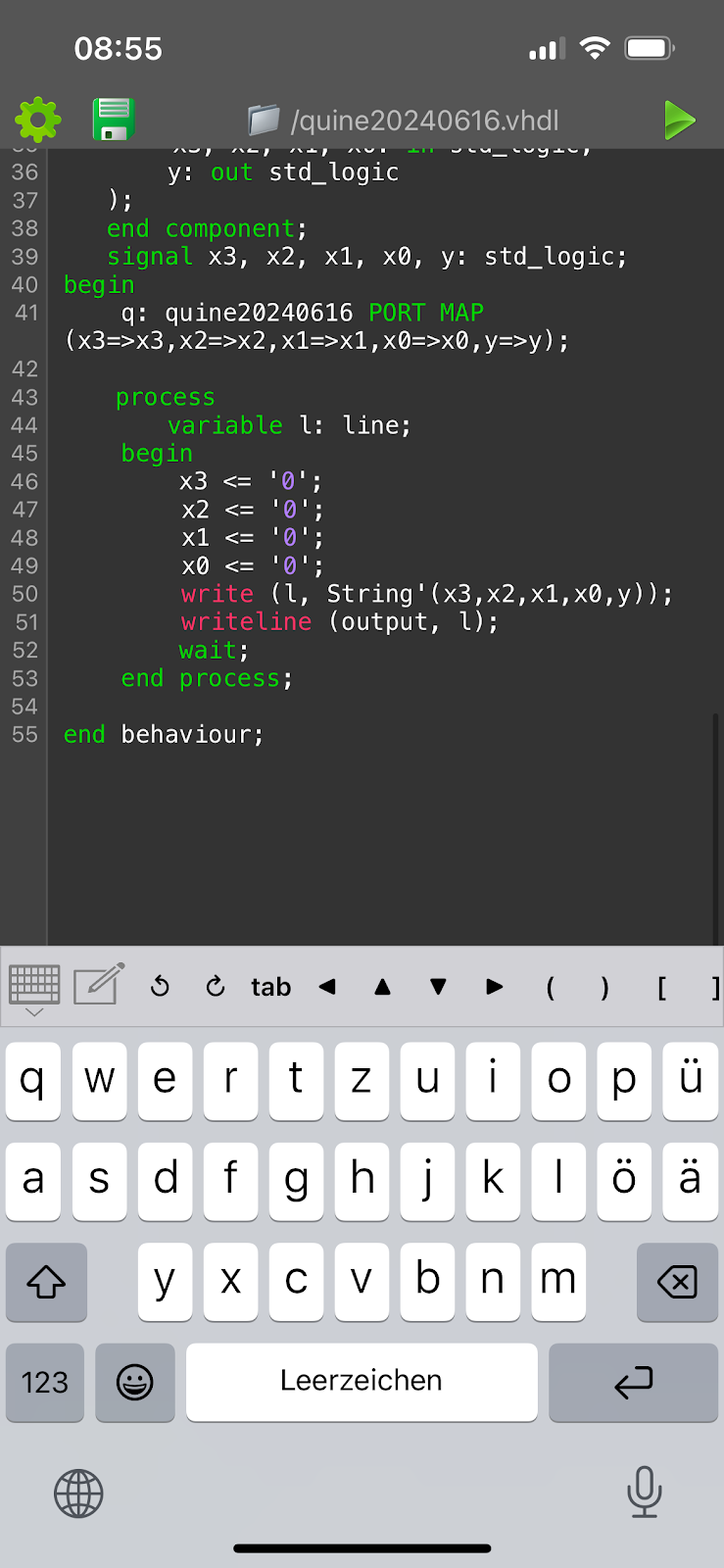

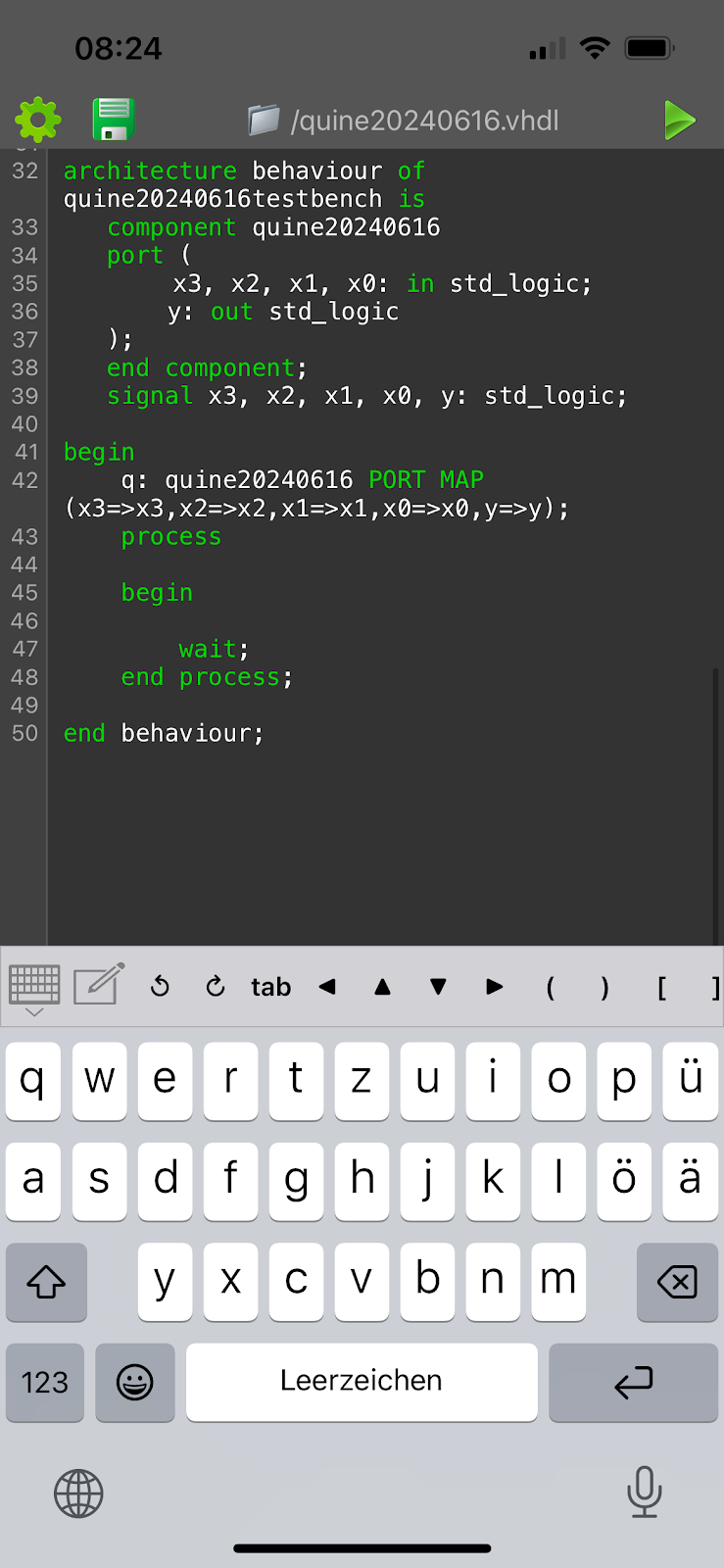

library ieee;

use ieee.std_logic_1164.all;

use std.textio.all;

entity quine20240616testbench is

end;

architecture behaviour of quine20240616testbench is

component quine20240616

port (

x3, x2, x1, x0: in std_logic;

y: out std_logic

);

end component;

signal x3, x2, x1, x0, y: std_logic;

begin

q: quine20240616 PORT MAP (x3=>x3,x2=>x2,x1=>x1,x0=>x0,y=>y);

process

variable l: line;

begin

x3 <= '0';

x2 <= '0';

x1 <= '0';

x0 <= '0';

write (l, String'(x3,x2,x1,x0,y));

writeline (output, l);

wait;

end process;

end behaviour;

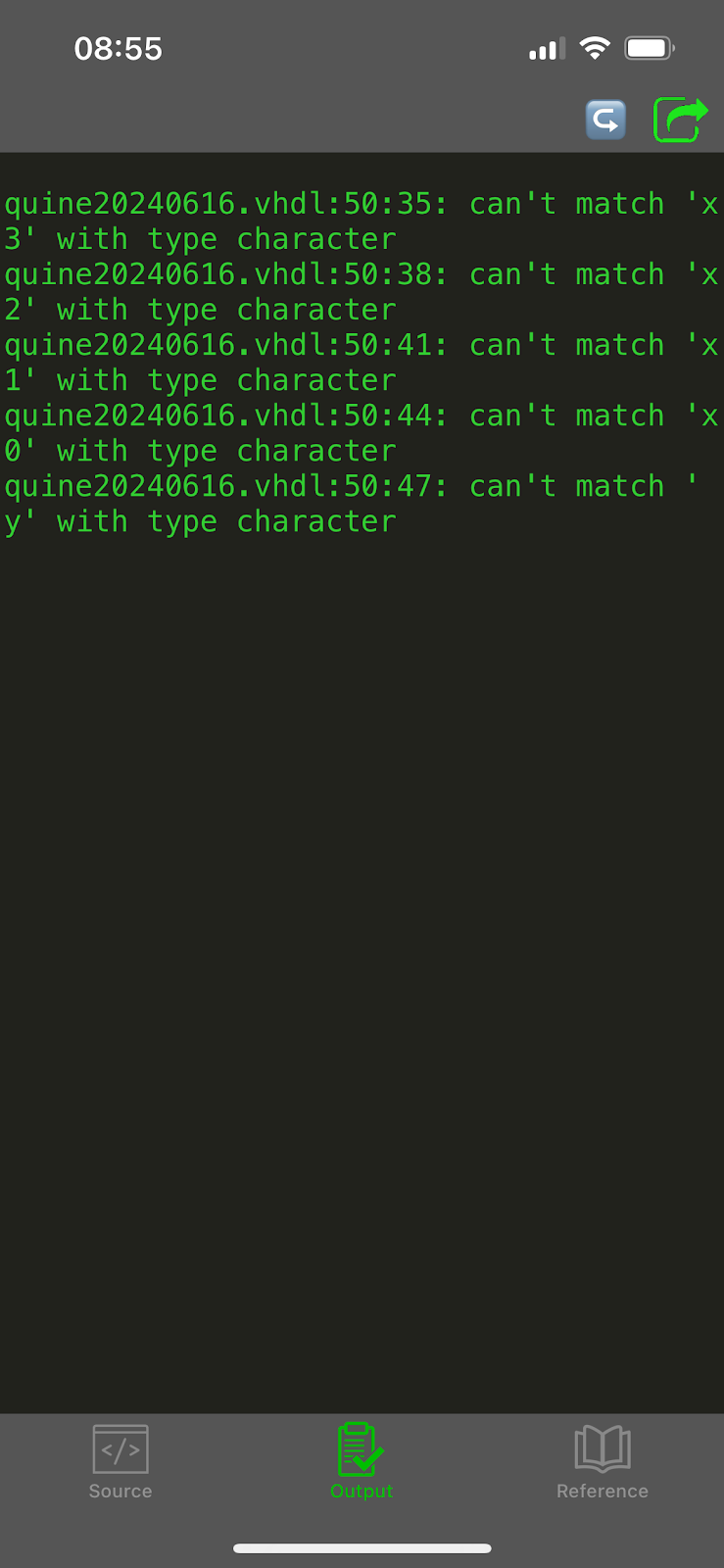

So, da gibt es noch ein paar probleme bei vhdl ohne gtkwave. Ich weiss nicht, wie man mit write signale ausgibt, und: wie erziele ich dass genau eine komponente ausgefuehrt wird. Ich loese das problem wann anders

Ich muss jetzt die testbench neu schreiben, ich verwende dafuer ja bisher einen generator, der es fuer gtkwave macht. Deswegen jetzt mit write und ouput, aber das ist eine frage des generators.

Oder ich schreibe es ein mal und verwende es als template, vorlage ohne es jedes mal zu schreiben.

Oder noch besser, mit write brauche ich keine nanosekunden. Es ist ein process, aber danach wird jedes mal write ausgefuehrt

-- https://phpbb3.ituenix.de/viewtopic.php?p=2504\&sid=fe31b12ff2b3b374eaca692913acc42d#p2504

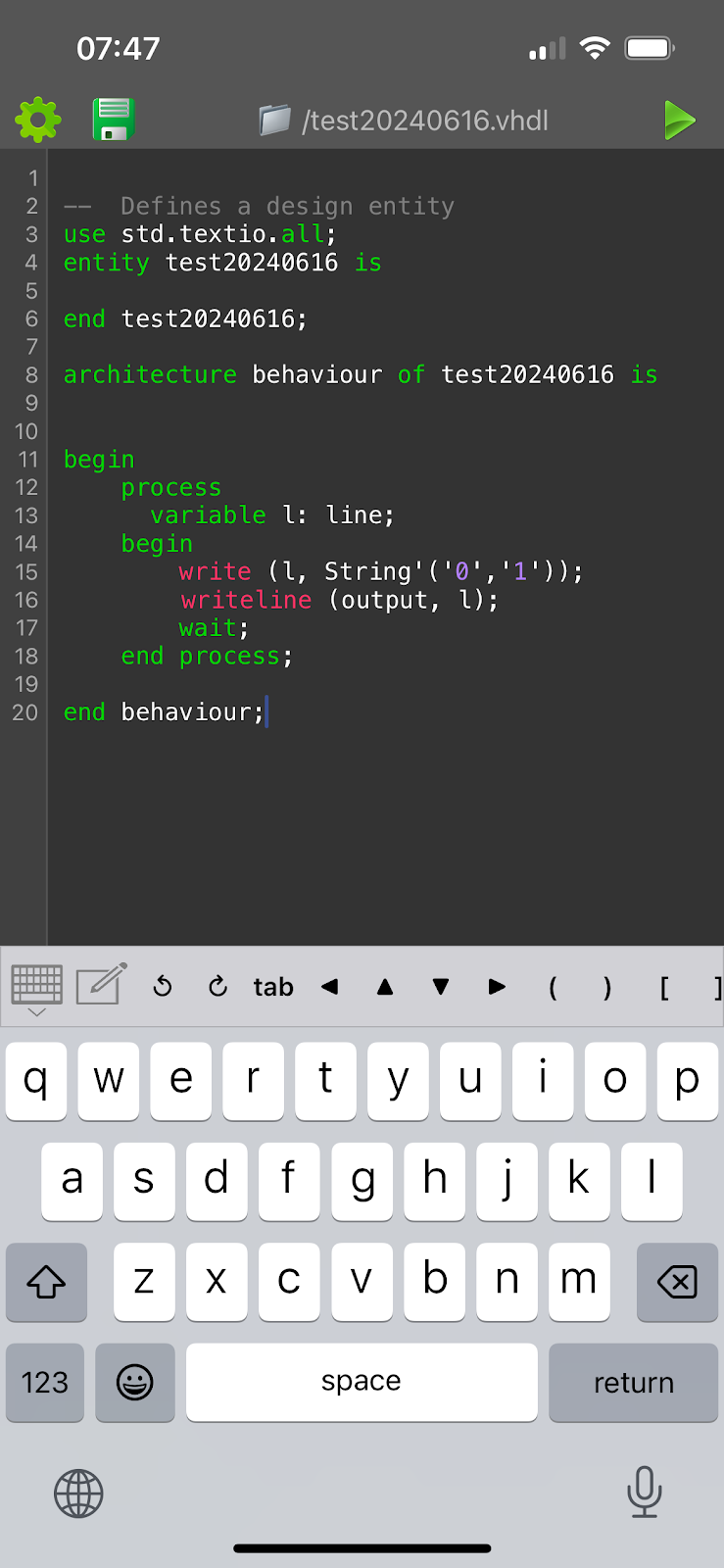

-- Defines a design entity

use std.textio.all;

entity test20240616 is

end test20240616;

architecture behaviour of test20240616 is

begin

process

variable l: line;

begin

write (l, String'('0','1'));

writeline (output, l);

wait;

end process;

end behaviour;

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

0:1 0 0 0 -

0:2 0 0 - 0

0:8 - 0 0 0

2:10 - 0 1 0

8:10 1 0 - 0

8:12 1 - 0 0

10:11 1 0 1 -

7:15 - 1 1 1

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

0:2 0 0 - 0

8:10 1 0 - 0

0:8 - 0 0 0

2:10 - 0 1 0

7:15 - 1 1 1

8:12 1 - 0 0

11:15 1 - 1 1

Gruppe 0:

0:1 0 0 0 -

Gruppe 2:

10:11 1 0 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

8:10 1 0 - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

2:10 - 0 1 0

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 3:

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

8:10 1 0 - 0

0:2:8:10 - 0 - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

2:10 - 0 1 0

0:8:2:10 - 0 - 0

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 3:

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

0:2:8:10 - 0 - 0

7:15 - 1 1 1

8:12 1 - 0 0

11:15 1 - 1 1

Primimplikantentafel

0 1 2 7 8 10 11 12 15

0:1 * *

10:11 * *

0:2:8:10 * * * *

7:15 * *

8:12 * *

11:15 * *

0 1 2 7 8 10 11 12 15

0:1 * * p

10:11 * *

0:2:8:10 * * * * p

7:15 * * p

8:12 * * p

11:15 * *

0 1 2 7 8 10 11 12 15

0:1 * * p

10:11 * *

0:2:8:10 * * * * p

7:15 * * p

8:12 * * p

0:1 0 0 0 -

10:11 1 0 1 -

0:2:8:10 - 0 - 0

7:15 - 1 1 1

8:12 1 - 0 0

y <= (not x3 and not x2 and not x1) or

(x3 and not x2 or x1) or

(not x2 or not x0) or

(x2 and x1 and x0) or

(x3 and not x1 and not x0)

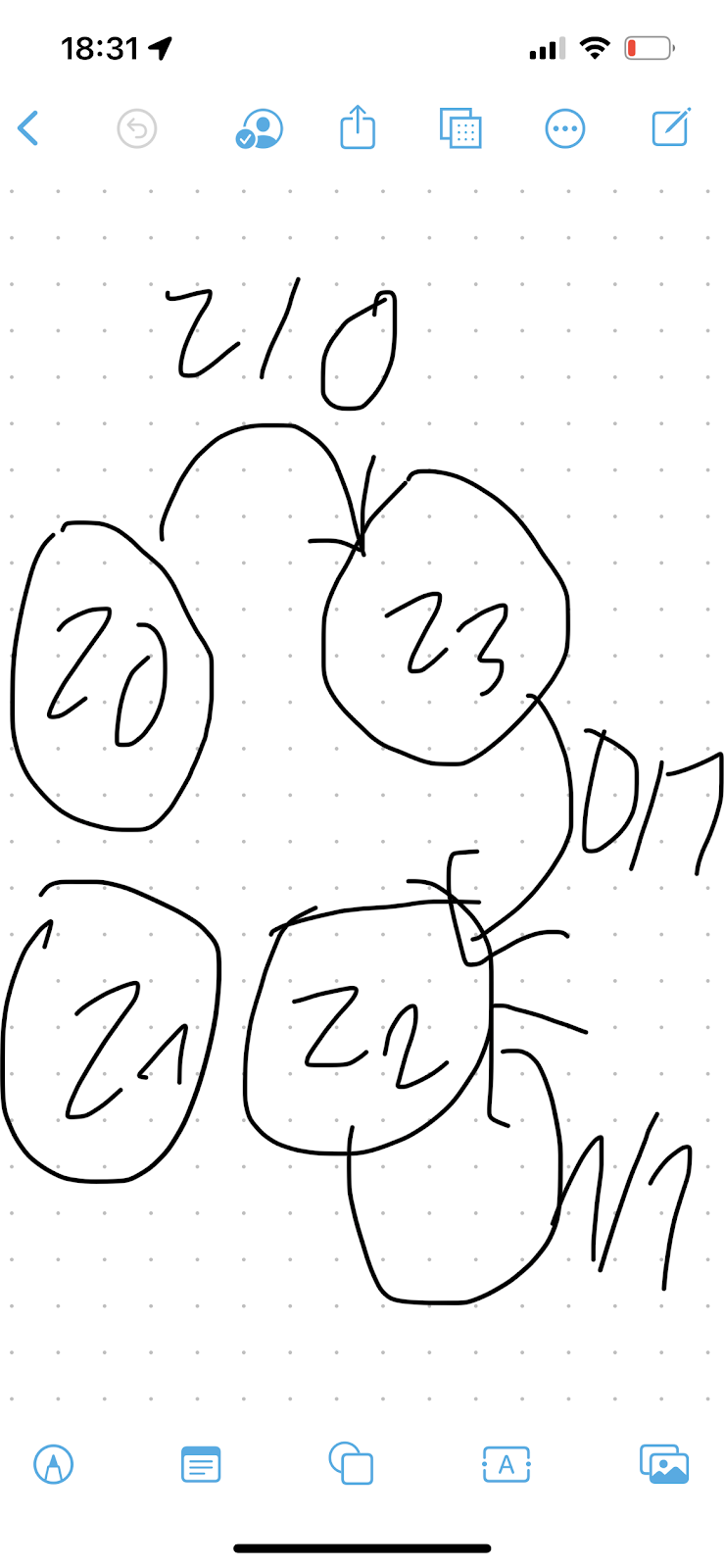

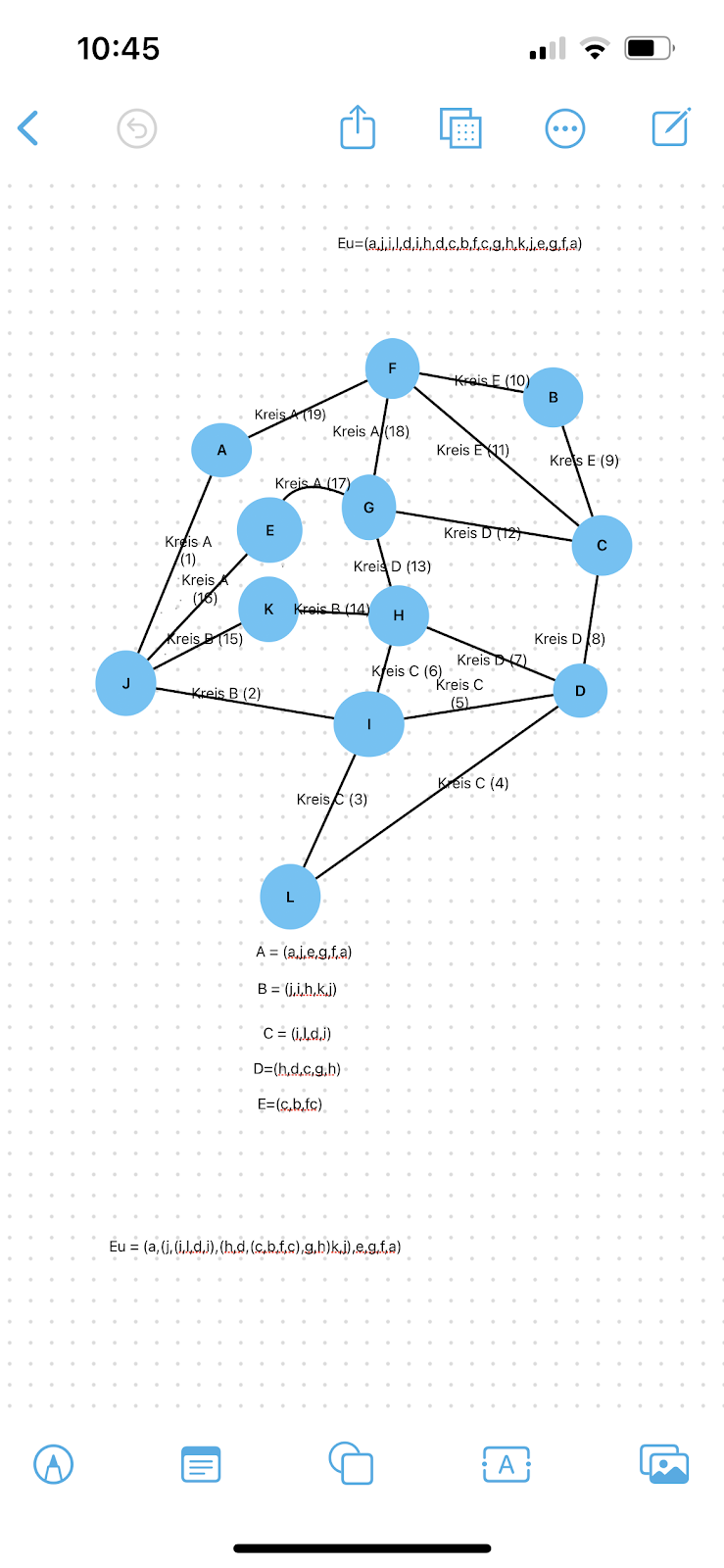

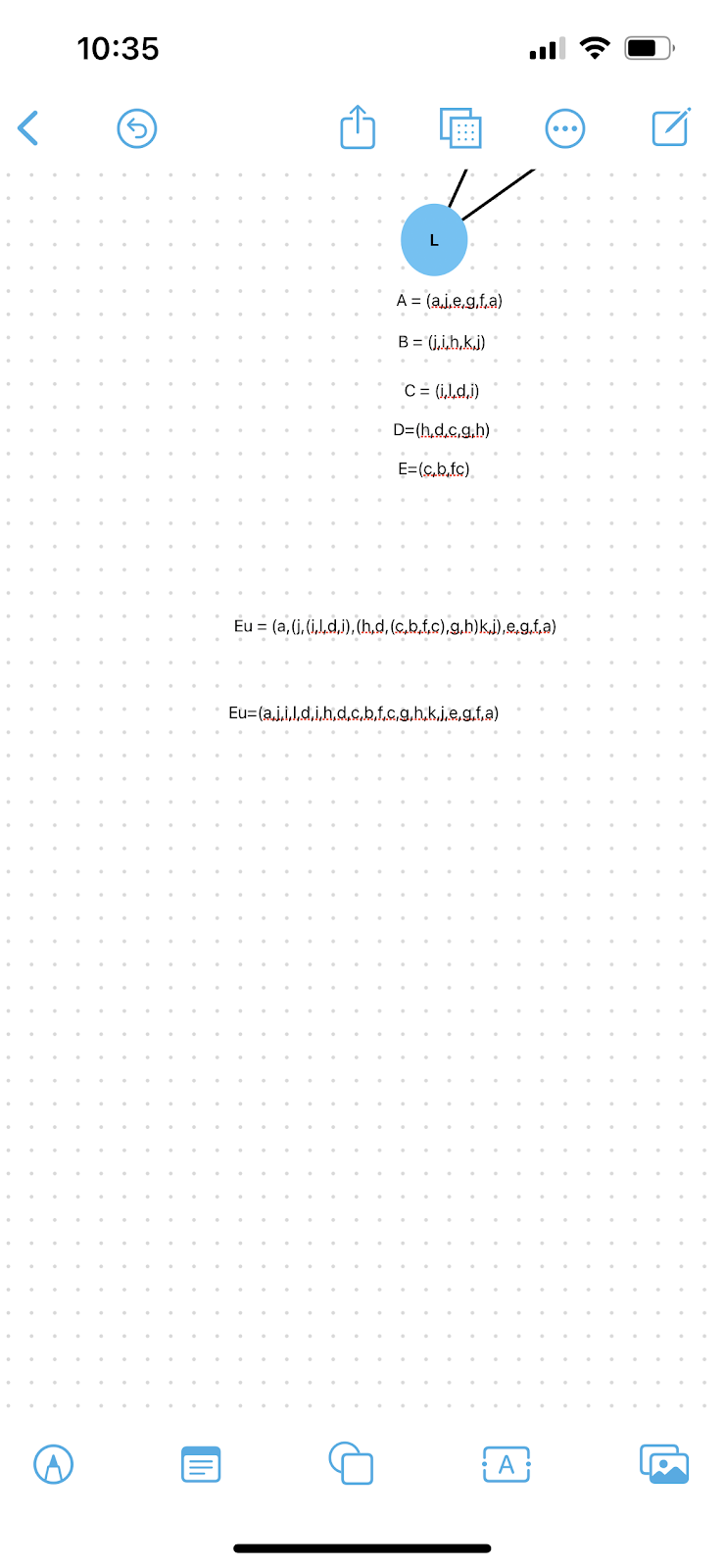

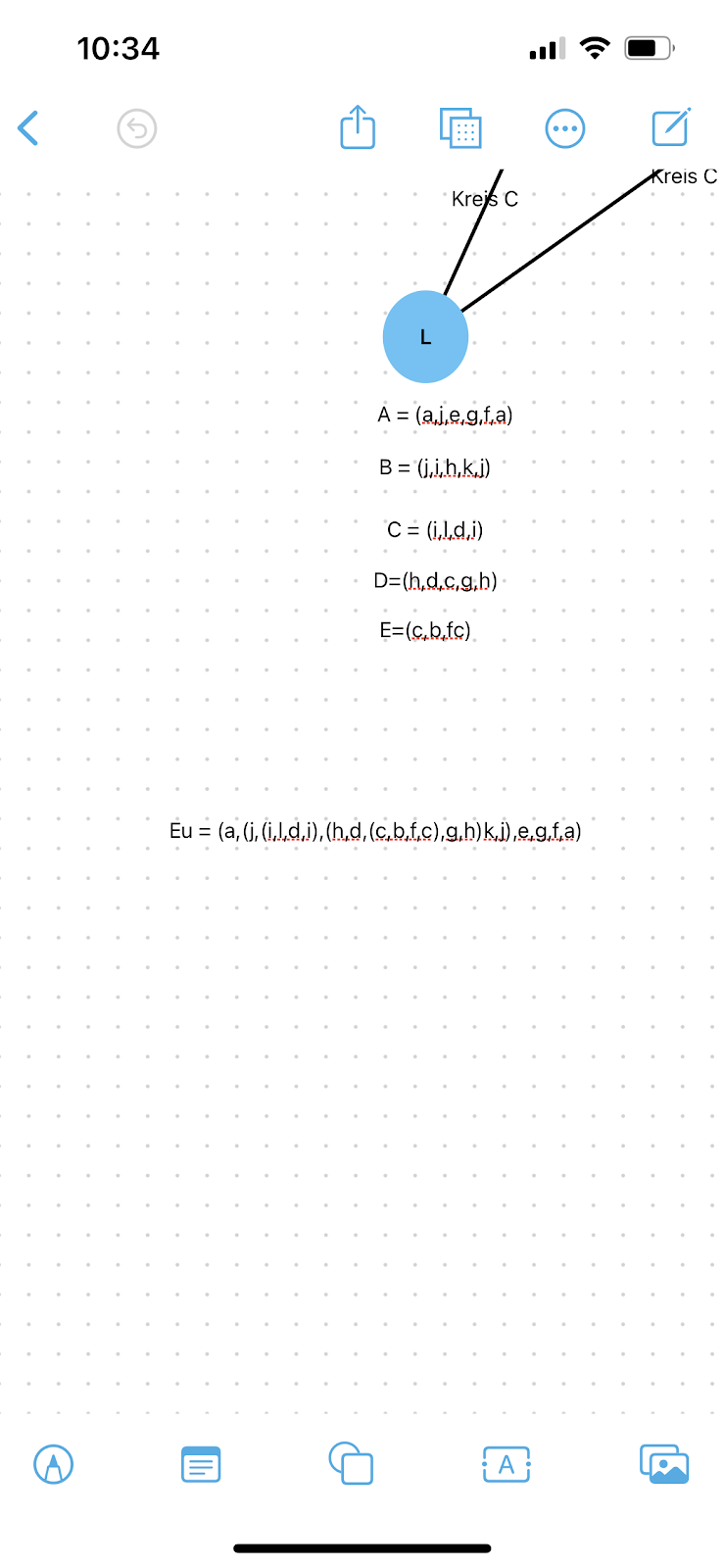

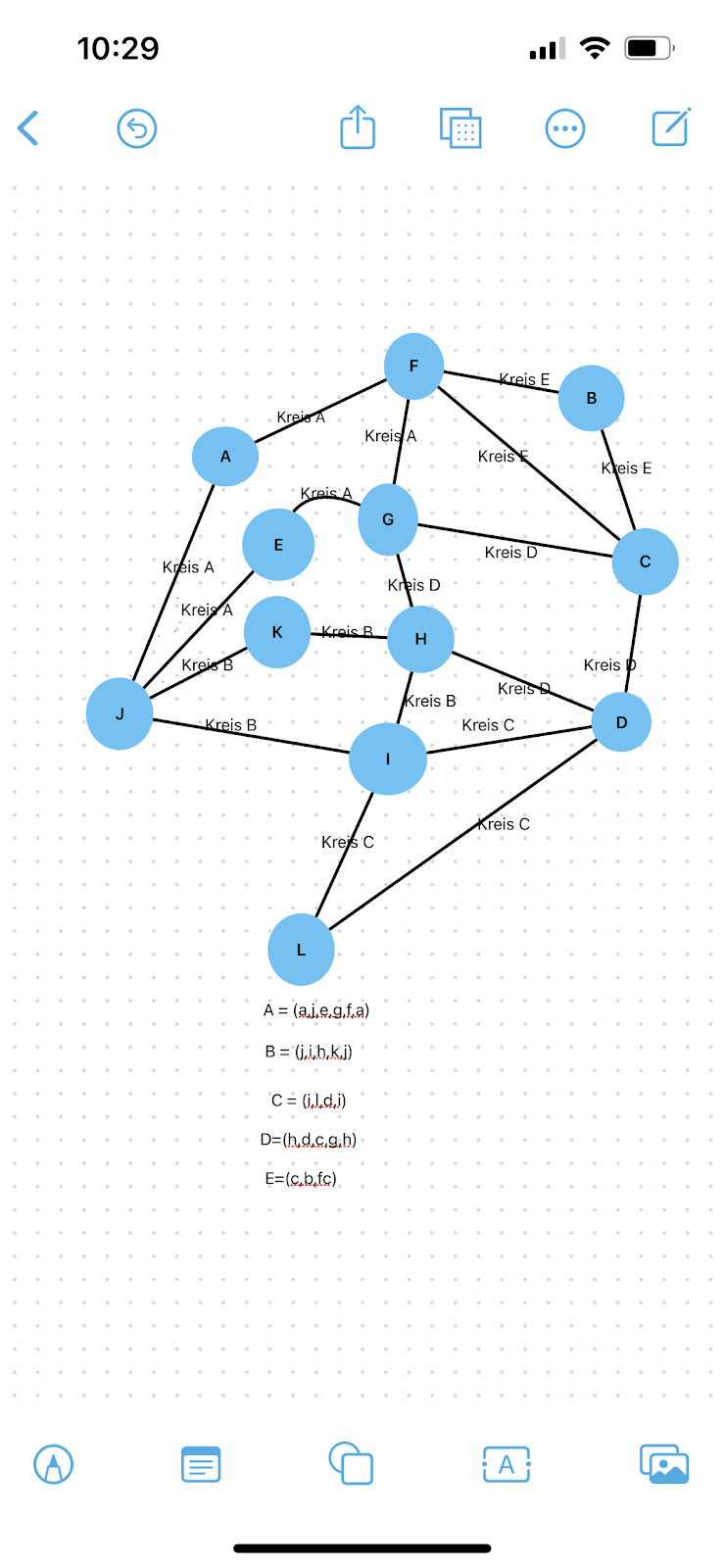

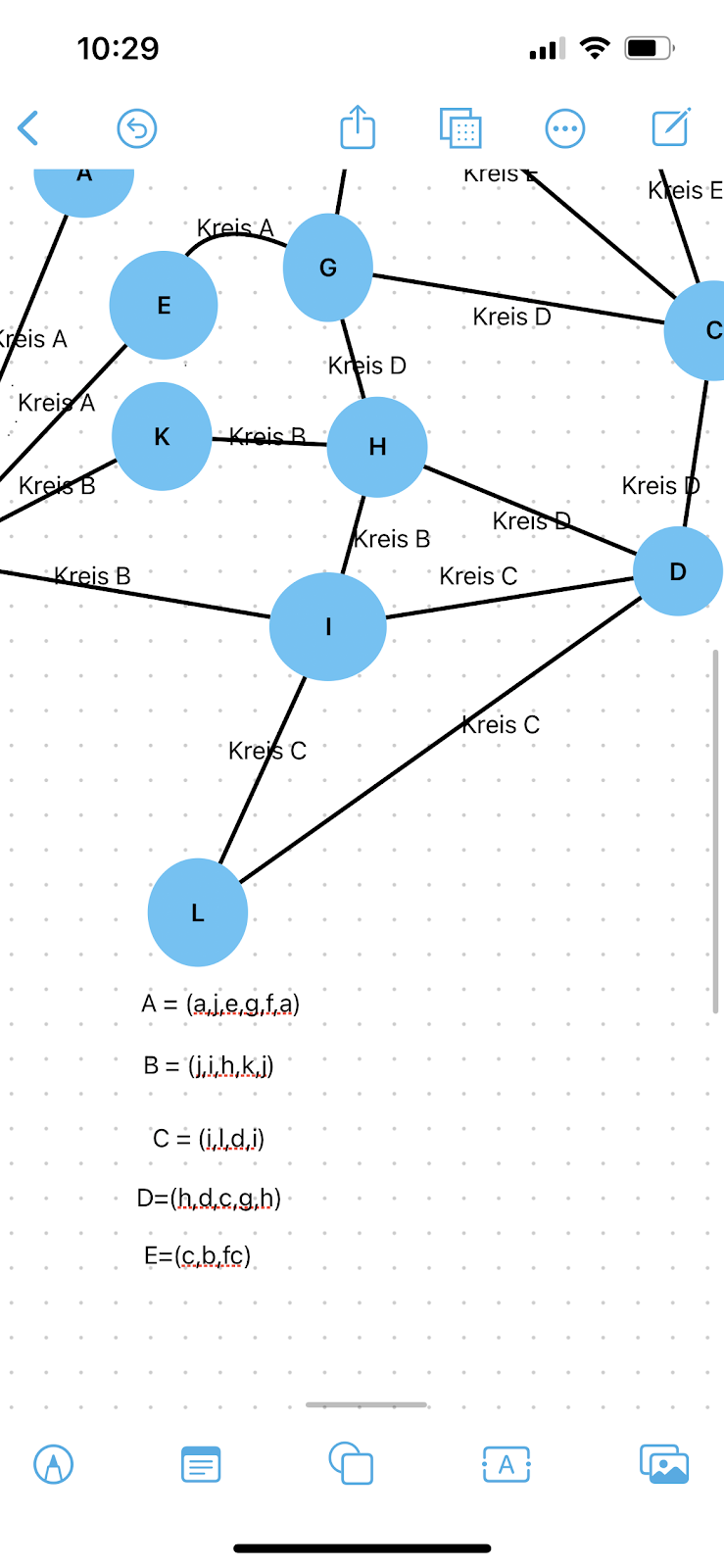

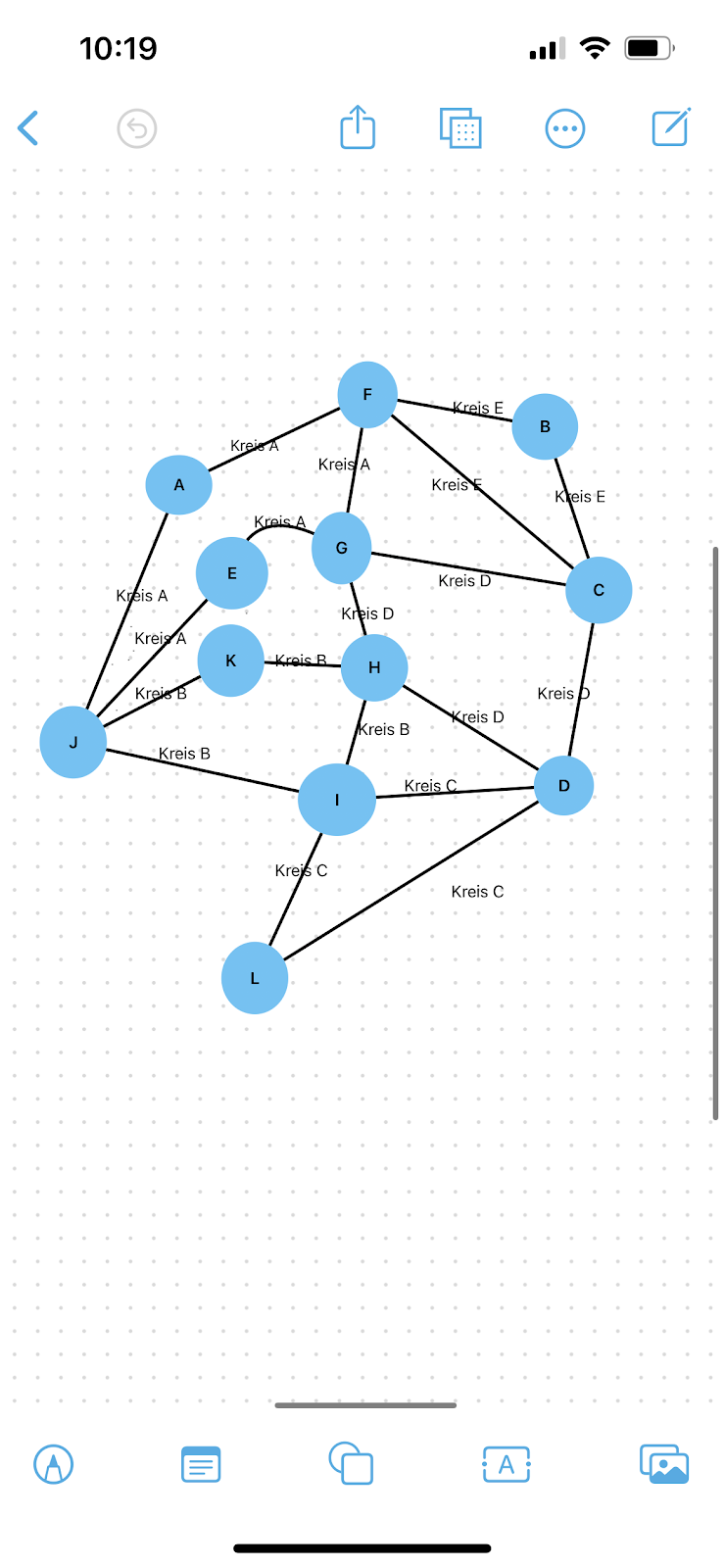

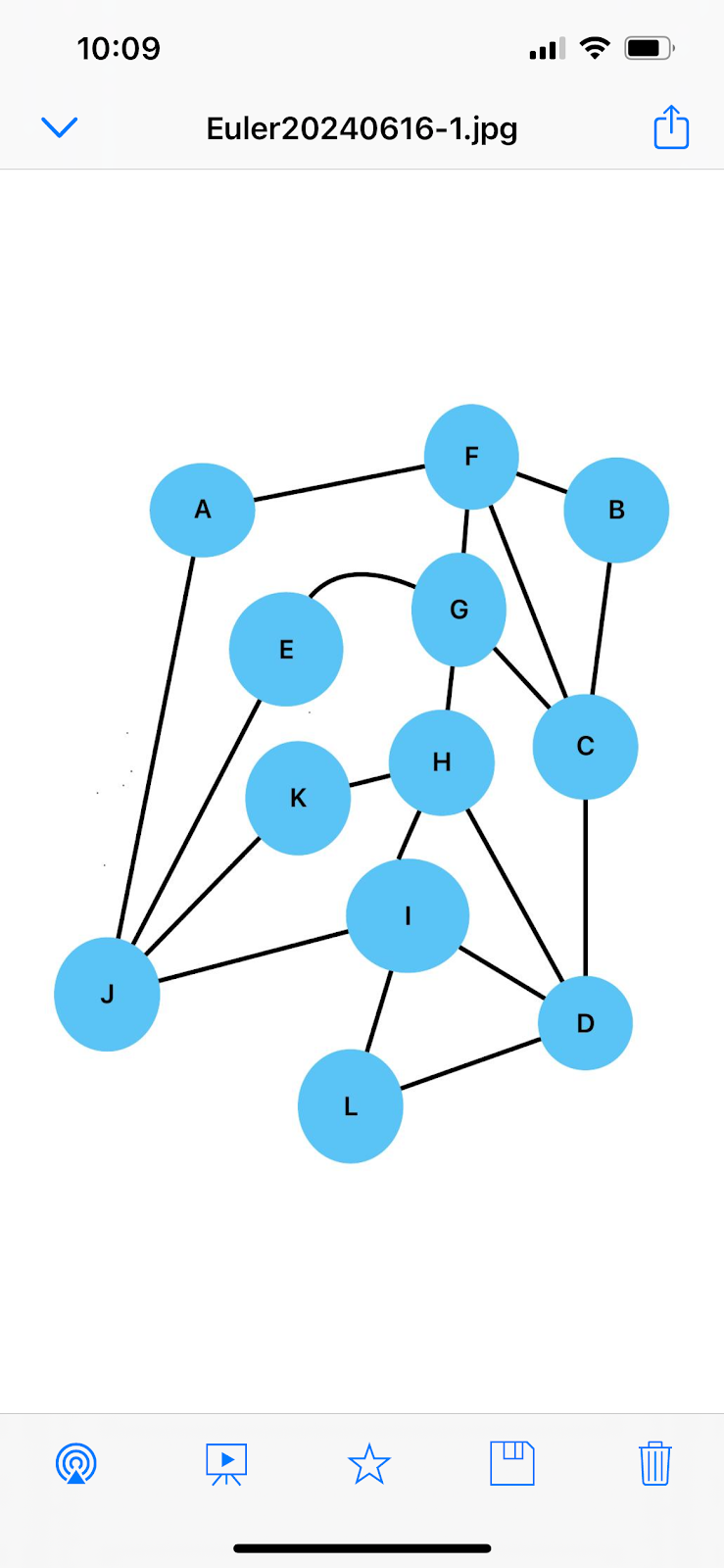

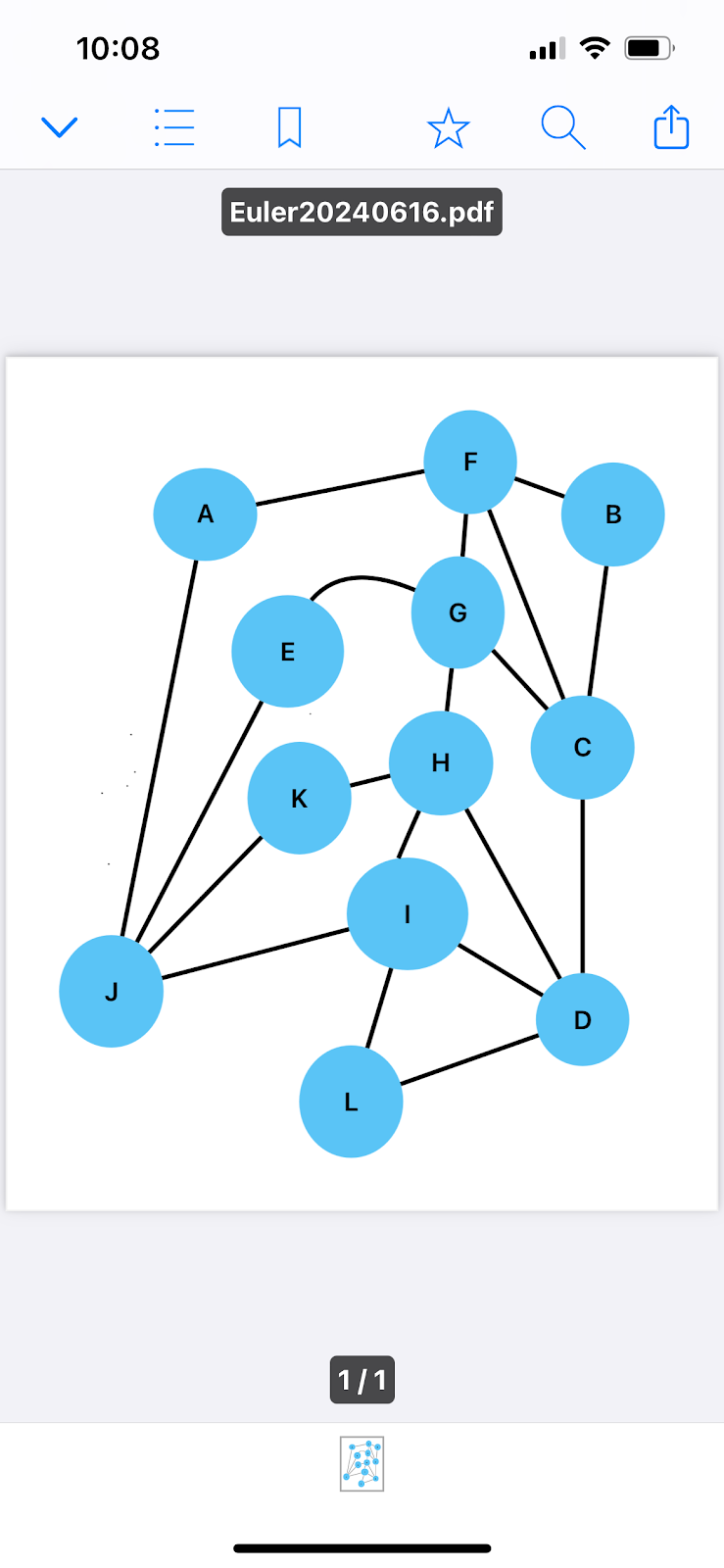

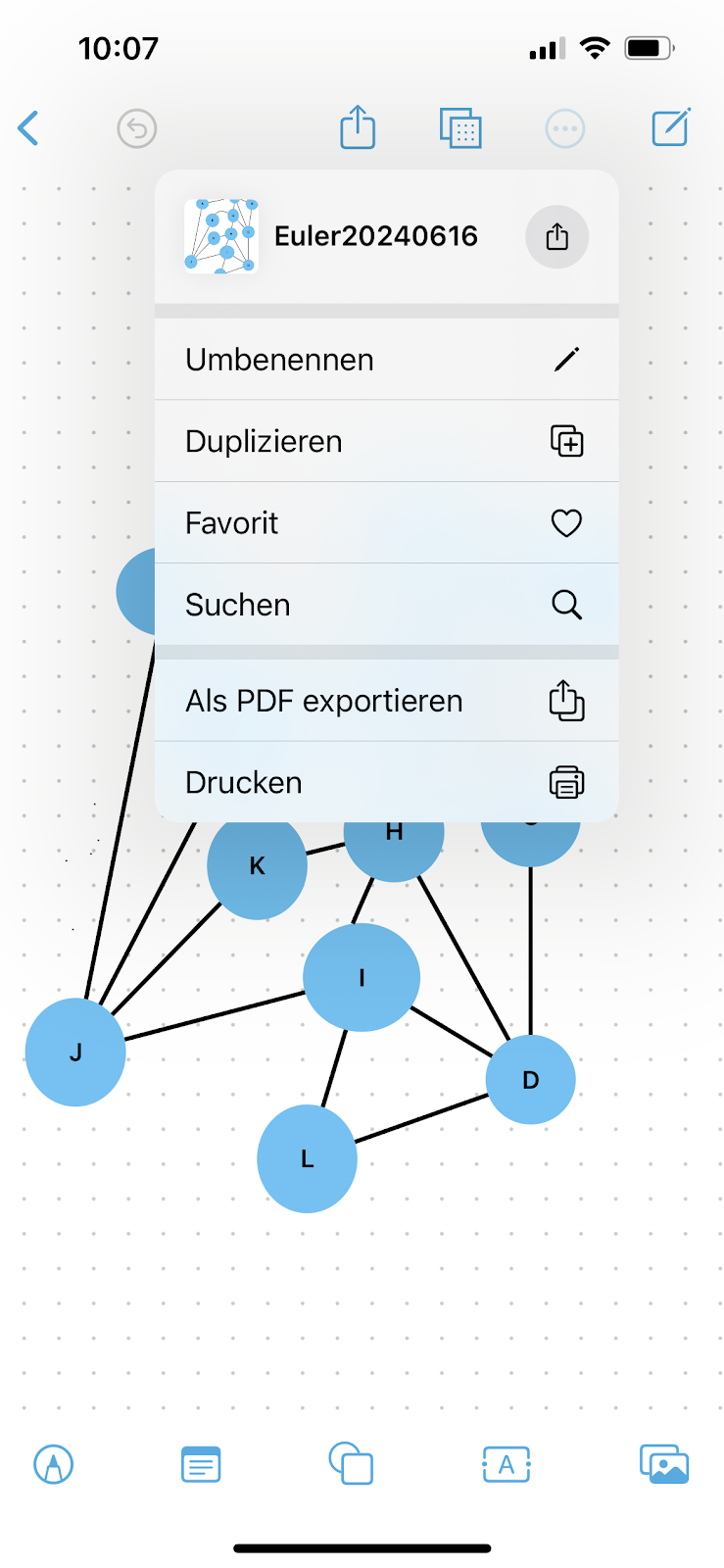

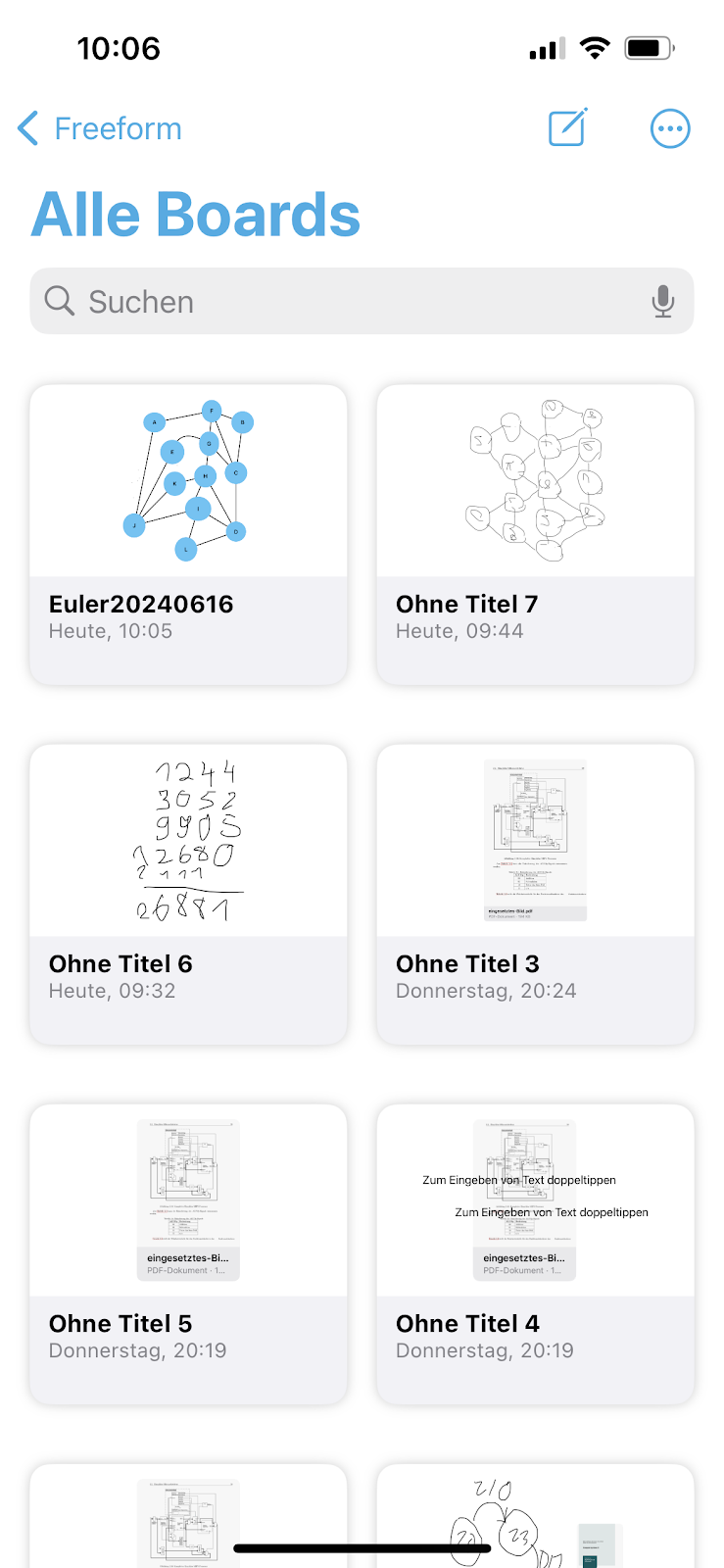

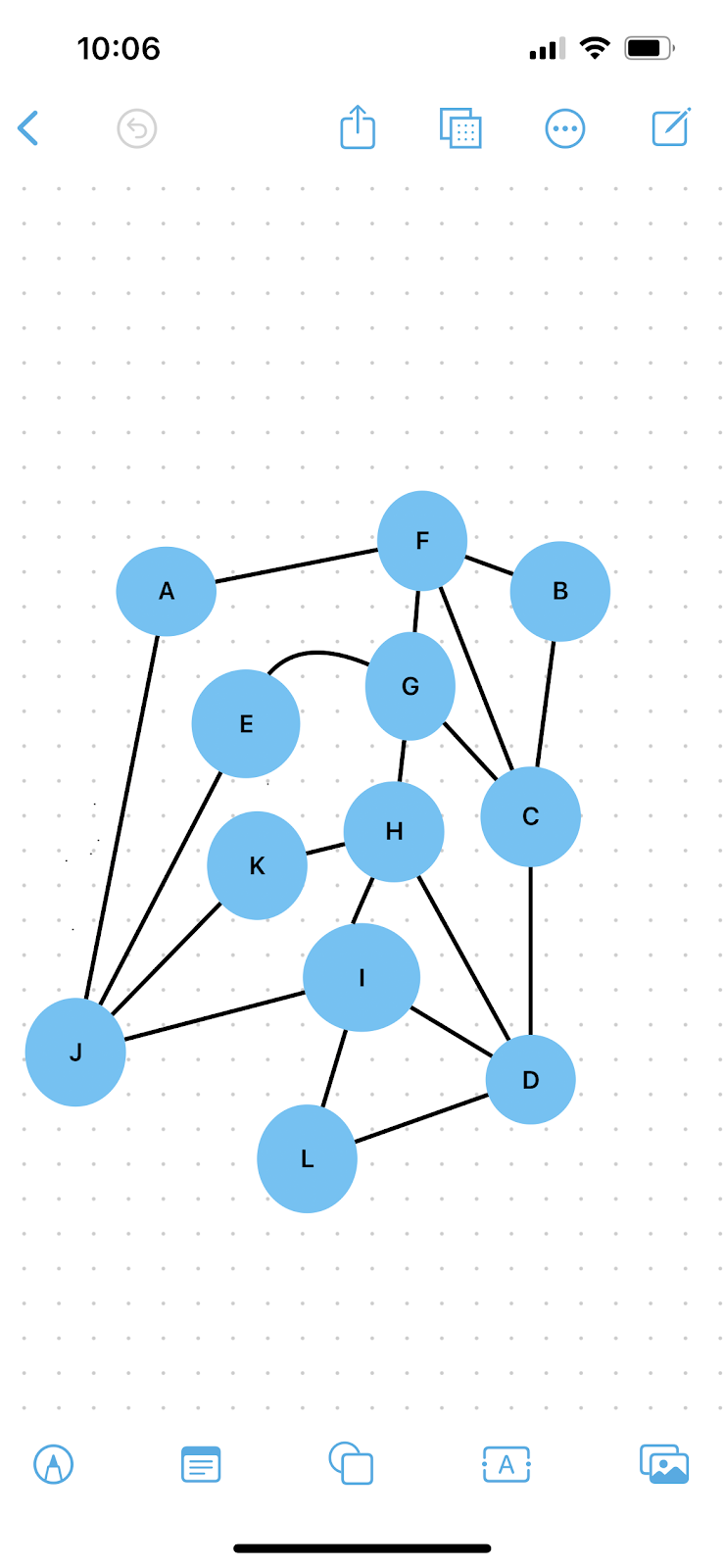

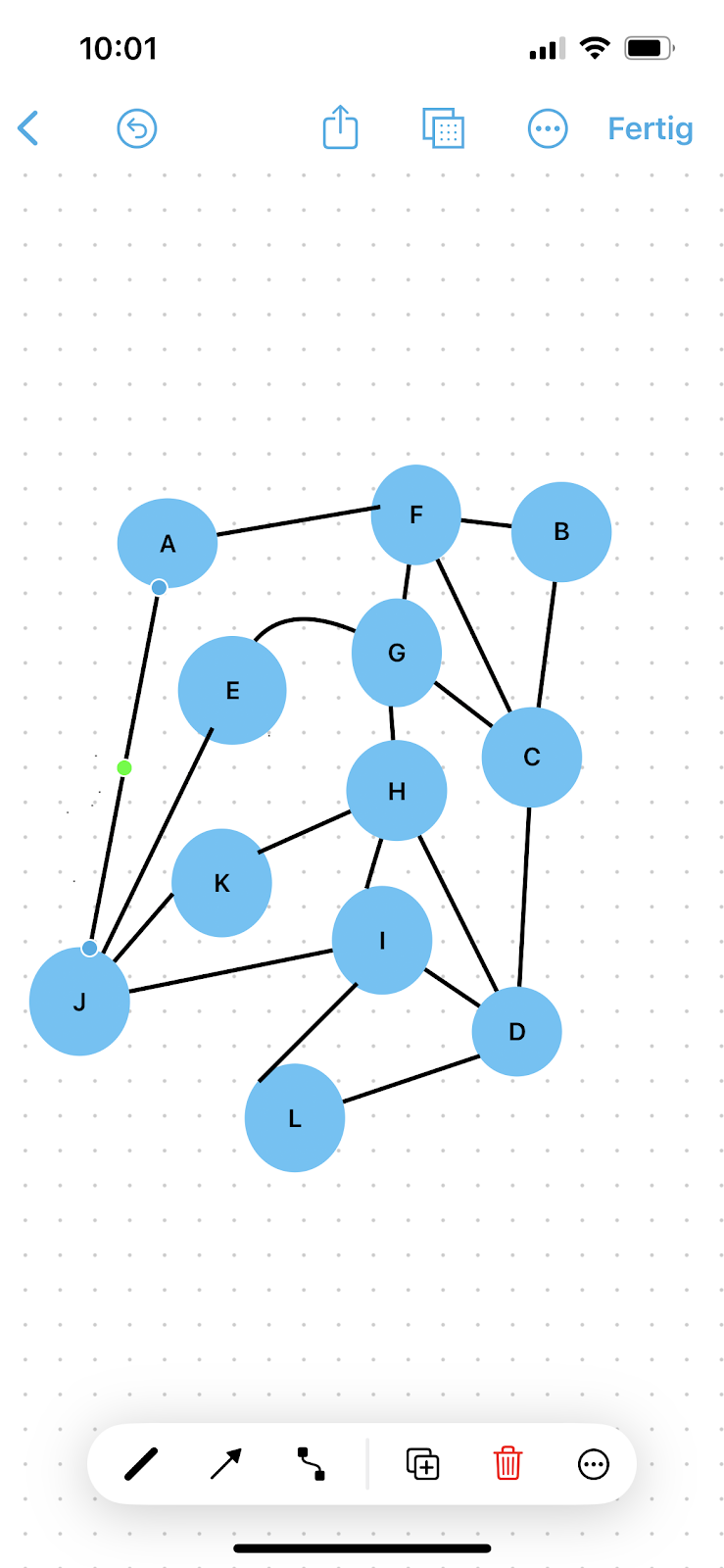

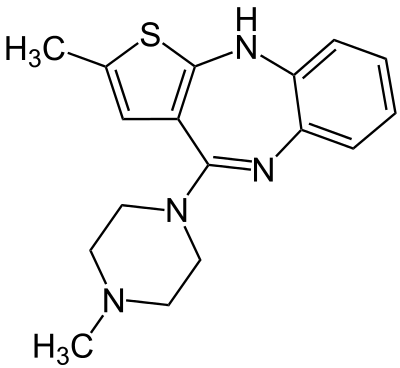

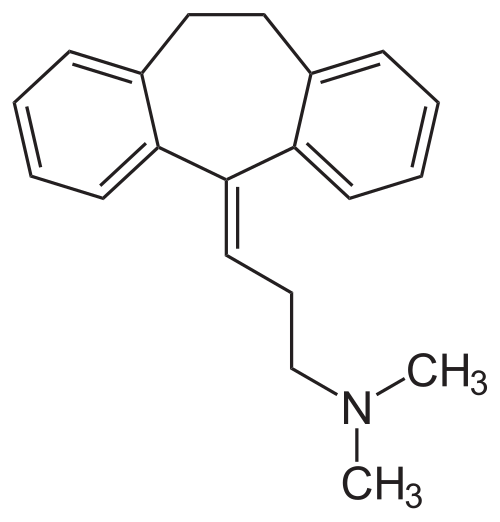

Ich habe mir ueberlegt ob ich tuebingen eine mache. Ich suche mir ein paar punkte raus. Und suche nach wegen, wo ich zwischen nicht drei punkten zwingend den selben laufe, also: wenn ich sehe, hier war ich noch nicht, aber war auf jeder kante bzw. strecke, die ich meinte, dann war es eine

Machen wir eine eulertour? Das eine ist olanzapin, das andere ein trizyklisches as antideptressivum und sie werden sehen, es geht nicht. Weil es gehen drei kanten raus

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

3 0 0 1 1 0

4 0 1 0 0 0

5 0 1 0 1 0

6 0 1 1 0 0

7 0 1 1 1 1

8 1 0 0 0 1

9 1 0 0 1 0

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

13 1 1 0 1 0

14 1 1 1 0 0

15 1 1 1 1 1

0 0 0 0 0 1

1 0 0 0 1 1

2 0 0 1 0 1

7 0 1 1 1 1

8 1 0 0 0 1

10 1 0 1 0 1

11 1 0 1 1 1

12 1 1 0 0 1

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

Gruppe 0:

0 0 0 0 0 1

Gruppe 1:

1 0 0 0 1 1

2 0 0 1 0 1

8 1 0 0 0 1

Gruppe 2:

10 1 0 1 0 1

12 1 1 0 0 1

Gruppe 3:

7 0 1 1 1 1

11 1 0 1 1 1

Gruppe 4:

15 1 1 1 1 1

0:1 0 0 0 -

0:2 0 0 - 0

0:8 - 0 0 0

2:10 - 0 1 0

8:10 1 0 - 0

8:12 1 - 0 0

10:11 1 0 1 -

7:15 - 1 1 1

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

0:2 0 0 - 0

8:10 1 0 - 0

0:8 - 0 0 0

2:10 - 0 1 0

7:15 - 1 1 1

8:12 1 - 0 0

11:15 1 - 1 1

Gruppe 0:

0:1 0 0 0 -

Gruppe 2:

10:11 1 0 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

8:10 1 0 - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

2:10 - 0 1 0

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 3:

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

Gruppe 0:

0:2 0 0 - 0

Gruppe 1:

8:10 1 0 - 0

0:2:8:10 - 0 - 0

Gruppe 0:

0:8 - 0 0 0

Gruppe 1:

2:10 - 0 1 0

0:8:2:10 - 0 - 0

Gruppe 3:

7:15 - 1 1 1

Gruppe 1:

8:12 1 - 0 0

Gruppe 3:

11:15 1 - 1 1

0:1 0 0 0 -

10:11 1 0 1 -

0:2:8:10 - 0 - 0

7:15 - 1 1 1

8:12 1 - 0 0

11:15 1 - 1 1

Primimplikantentafel

0 1 2 7 8 10 11 12 15

0:1 * *

10:11 * *

0:2:8:10 * * * *

7:15 * *

8:12 *. *

11:15 *. *

0 1 2 7 8 10 11 12 15

0:1 * *

10:11 * *

0:2:8:10 * * * *

7:15 * *

8:12 *. *

0:1 0 0 0 -

10:11 1 0 1 -

0:2:8:10 - 0 - 0

7:15 - 1 1 1

8:12 1 - 0 0

y <= not x3 and not x2 and not x1

or (x3... spaeter weiter

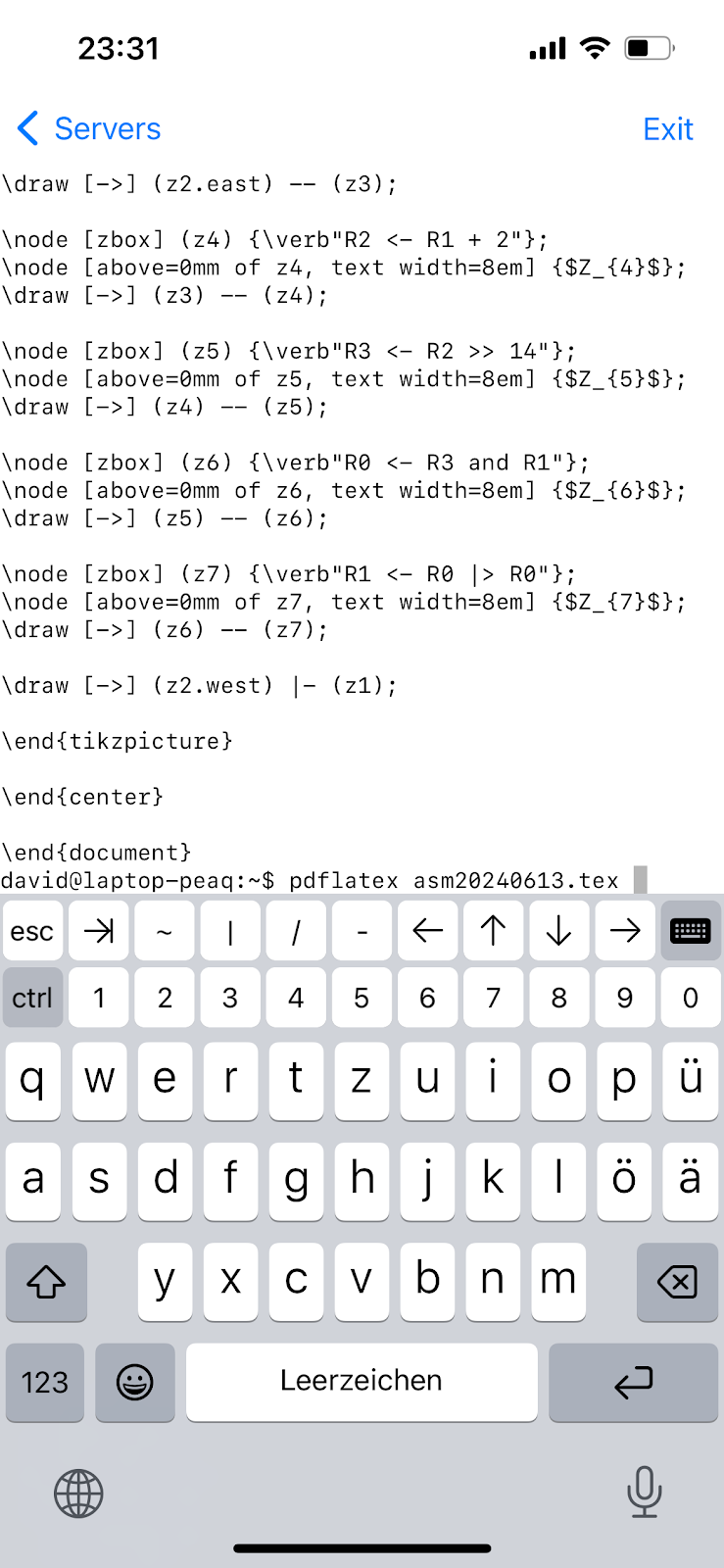

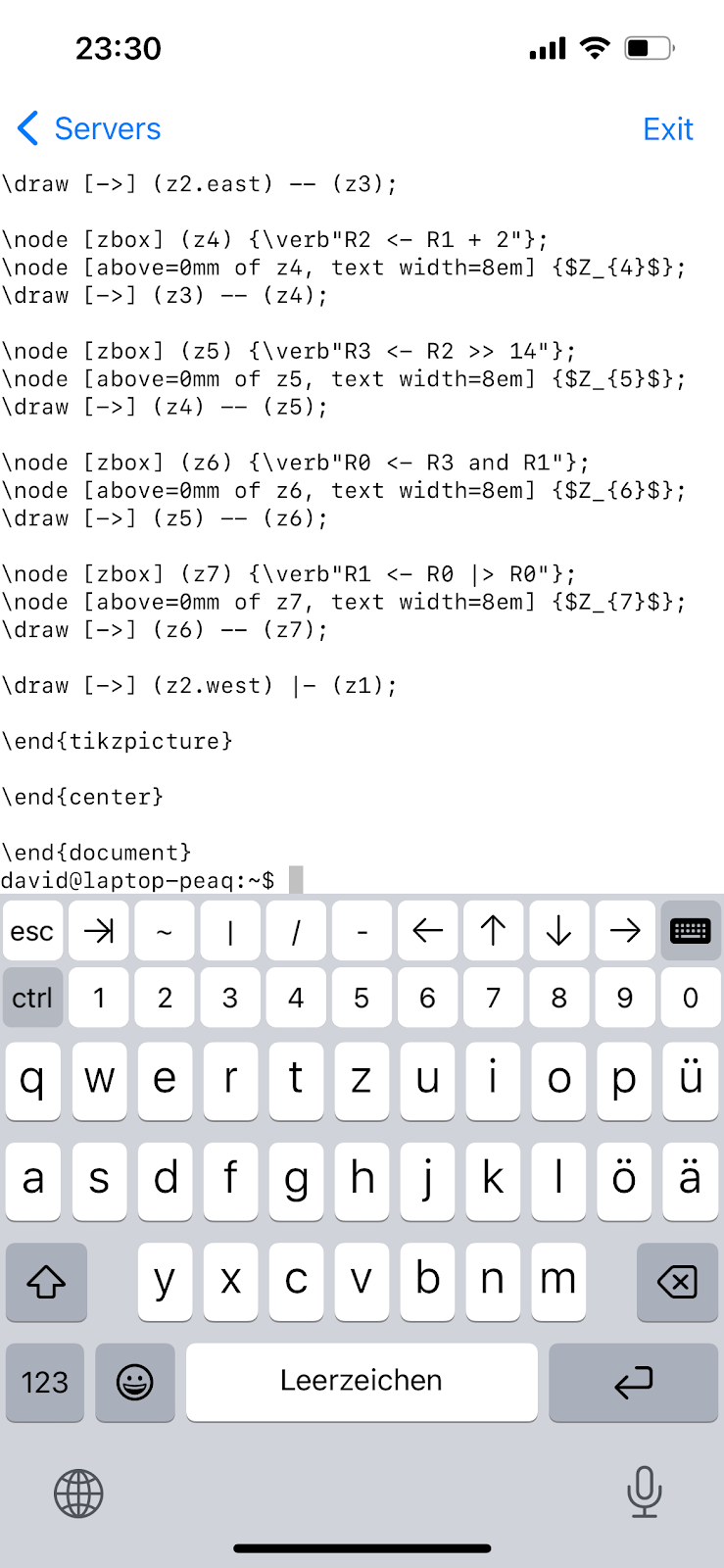

0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 1 3 0 0 1 1 0 4 0 1 0 0 0 5 0 1 0 1 0 6 0 1 1 0 0 7 0 1 1 1 1 8 1 0 0 0 1 9 1 0 0 1 0 10 1 0 1 0 1 11 1 0 1 1 1 12 1 1 0 0 1 13 1 1 0 1 0 14 1 1 1 0 0 15 1 1 1 1 1 0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 1 7 0 1 1 1 1 8 1 0 0 0 1 10 1 0 1 0 1 11 1 0 1 1 1 12 1 1 0 0 1 15 1 1 1 1 1 Gruppe 0: 0 0 0 0 0 1 Gruppe 1: 1 0 0 0 1 1 2 0 0 1 0 1 8 1 0 0 0 1 Gruppe 2: 10 1 0 1 0 1 12 1 1 0 0 1 Gruppe 3: 7 0 1 1 1 1 11 1 0 1 1 1 Gruppe 4: 15 1 1 1 1 1 Gruppe 0: 0 0 0 0 0 1 Gruppe 1: 1 0 0 0 1 1 2 0 0 1 0 1 8 1 0 0 0 1 Gruppe 2: 10 1 0 1 0 1 12 1 1 0 0 1 Gruppe 3: 7 0 1 1 1 1 11 1 0 1 1 1 Gruppe 4: 15 1 1 1 1 1 0:1 0 0 0 - 0:2 0 0 - 0 0:8 - 0 0 0 2:10 - 0 1 0 8:10 1 0 - 0 8:12 1 - 0 0 10:11 1 0 1 - 7:15 - 1 1 1 11:15 1 - 1 1 0:1 0 0 0 - 10:11 1 0 1 - 0:2 0 0 - 0 8:10 1 0 - 0 0:8 - 0 0 0 2:10 - 0 1 0 7:15 - 1 1 1 8:12 1 - 0 0 11:15 1 - 1 1 Gruppe 0: 0:1 0 0 0 - Gruppe 2: 10:11 1 0 1 - Gruppe 0: 0:2 0 0 - 0 Gruppe 1: 8:10 1 0 - 0 Gruppe 0: 0:8 - 0 0 0 Gruppe 1: 2:10 - 0 1 0 Gruppe 3: 7:15 - 1 1 1 Gruppe 1: 8:12 1 - 0 0 Gruppe 3: 11:15 1 - 1 1 0:1 0 0 0 - 10:11 1 0 1 - Gruppe 0: 0:2 0 0 - 0 Gruppe 1: 8:10 1 0 - 0 0:2:8:10 - 0 - 0 Gruppe 0: 0:8 - 0 0 0 Gruppe 1: 2:10 - 0 1 0 0:8:2:10 - 0 - 0 Gruppe 3: 7:15 - 1 1 1 Gruppe 1: 8:12 1 - 0 0 Gruppe 3: 11:15 1 - 1 1 0:1 0 0 0 - 10:11 1 0 1 - 0:2:8:10 - 0 - 0 7:15 - 1 1 1 8:12 1 - 0 0 11:15 1 - 1 1

0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 1 3 0 0 1 1 0 4 0 1 0 0 0 5 0 1 0 1 0 6 0 1 1 0 0 7 0 1 1 1 1 8 1 0 0 0 1 9 1 0 0 1 0 10 1 0 1 0 1 11 1 0 1 1 1 12 1 1 0 0 1 13 1 1 0 1 0 14 1 1 1 0 0 15 1 1 1 1 1 0 0 0 0 0 1 1 0 0 0 1 1 2 0 0 1 0 1 7 0 1 1 1 1 8 1 0 0 0 1 10 1 0 1 0 1 11 1 0 1 1 1 12 1 1 0 0 1 15 1 1 1 1 1 Gruppe 0: 0 0 0 0 0 1 Gruppe 1: 1 0 0 0 1 1 2 0 0 1 0 1 8 1 0 0 0 1 Gruppe 2: 10 1 0 1 0 1 12 1 1 0 0 1 Gruppe 3: 7 0 1 1 1 1 11 1 0 1 1 1 Gruppe 4: 15 1 1 1 1 1 Gruppe 0: 0 0 0 0 0 1 Gruppe 1: 1 0 0 0 1 1 2 0 0 1 0 1 8 1 0 0 0 1 Gruppe 2: 10 1 0 1 0 1 12 1 1 0 0 1 Gruppe 3: 7 0 1 1 1 1 11 1 0 1 1 1 Gruppe 4: 15 1 1 1 1 1 0:1 0 0 0 - 0:2 0 0 - 0 0:8 - 0 0 0 2:10 - 0 1 0 8:10 1 0 - 0 8:12 1 - 0 0 10:11 1 0 1 - 7:15 - 1 1 1 11:15 1 - 1 1 0:1 0 0 0 - 10:11 1 0 1 - 0:2 0 0 - 0 8:10 1 0 - 0 0:8 - 0 0 0 2:10 - 0 1 0 7:15 - 1 1 1 8:12 1 - 0 0 11:15 1 - 1 1 Gruppe 0: 0:1 0 0 0 - Gruppe 2: 10:11 1 0 1 - Gruppe 0: 0:2 0 0 - 0 Gruppe 1: 8:10 1 0 - 0 Gruppe 0: 0:8 - 0 0 0 Gruppe 1: 2:10 - 0 1 0 Gruppe 3: 7:15 - 1 1 1 Gruppe 1: 8:12 1 - 0 0 Gruppe 3: 11:15 1 - 1 1 0:1 0 0 0 - 10:11 1 0 1 - Gruppe 0: 0:2 0 0 - 0 Gruppe 1: 8:10 1 0 - 0 0:2:8:10 - 0 - 0 Gruppe 0: 0:8 - 0 0 0 Gruppe 1: 2:10 - 0 1 0 0:8:2:10 - 0 - 0 Gruppe 3: 7:15 - 1 1 1 Gruppe 1: 8:12 1 - 0 0 Gruppe 3: 11:15 1 - 1 1 0:1 0 0 0 - 10:11 1 0 1 - 0:2:8:10 - 0 - 0 7:15 - 1 1 1 8:12 1 - 0 0 11:15 1 - 1 1

Den fpga mache ich heute abend. Vhdl mips32 immer sbends. Morgens lernen nachmittags aufgaben

Ich lerne auch auswendig. Jetzt. Ich lerne auch wieder computersysteme. Mit dem eineb smartphone filme ich, an dem anderen lese ich.

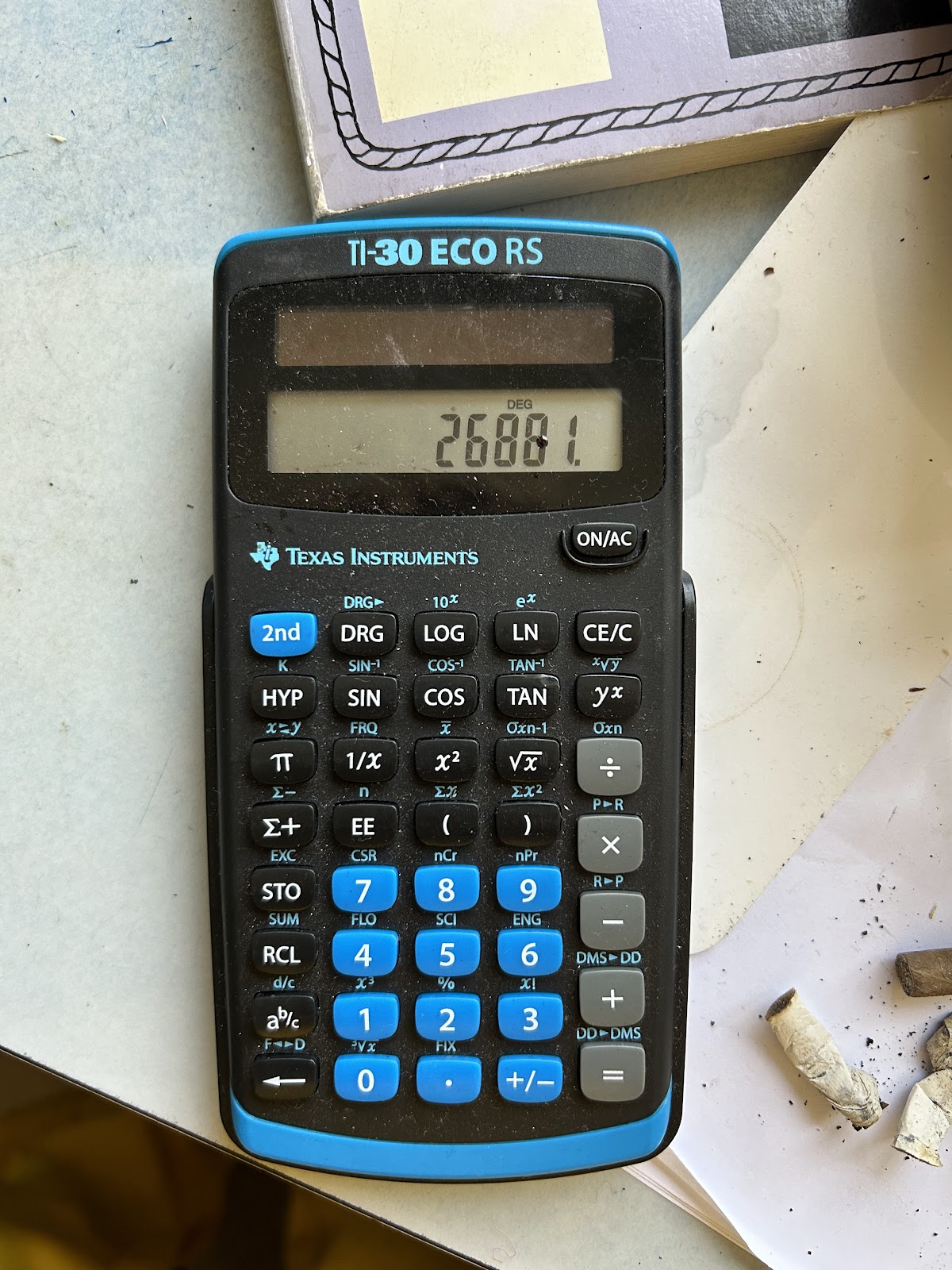

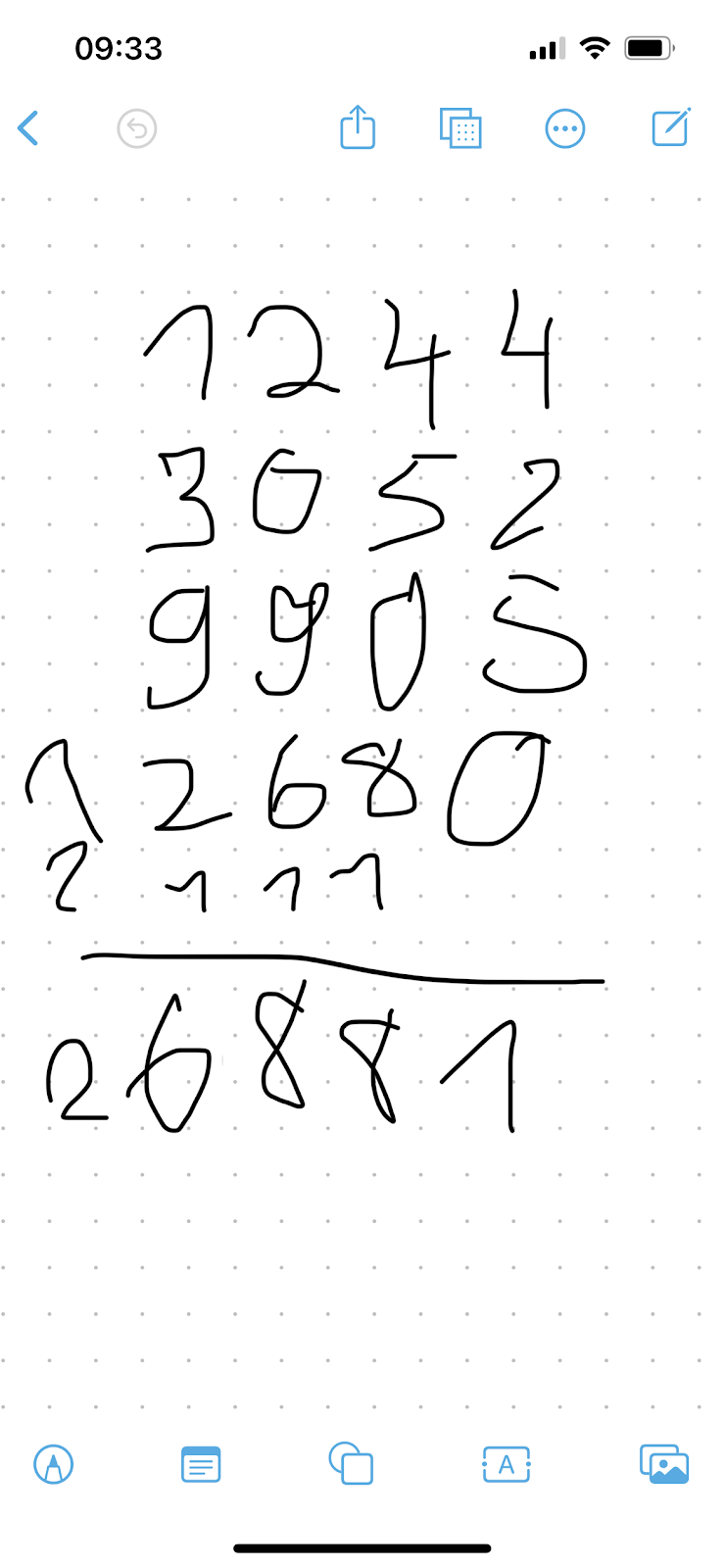

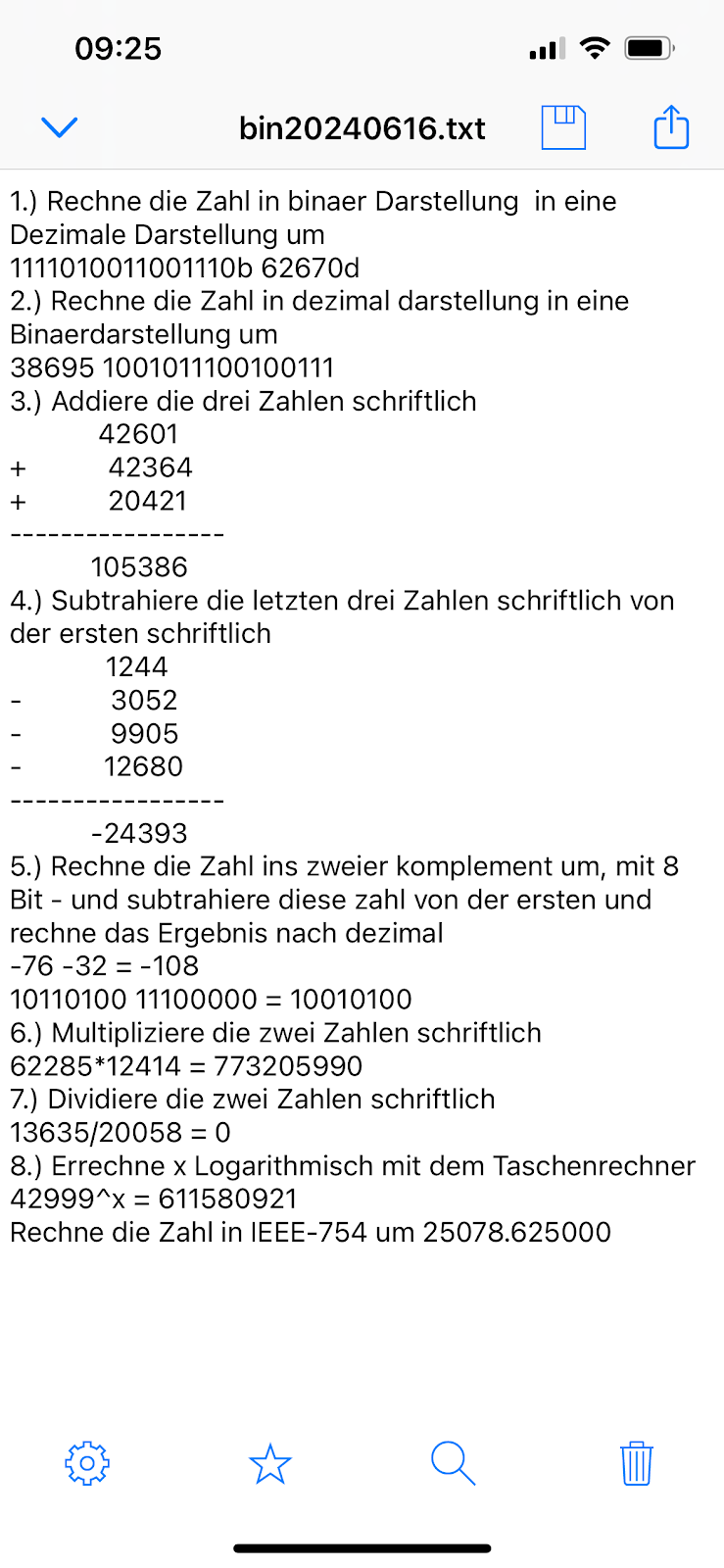

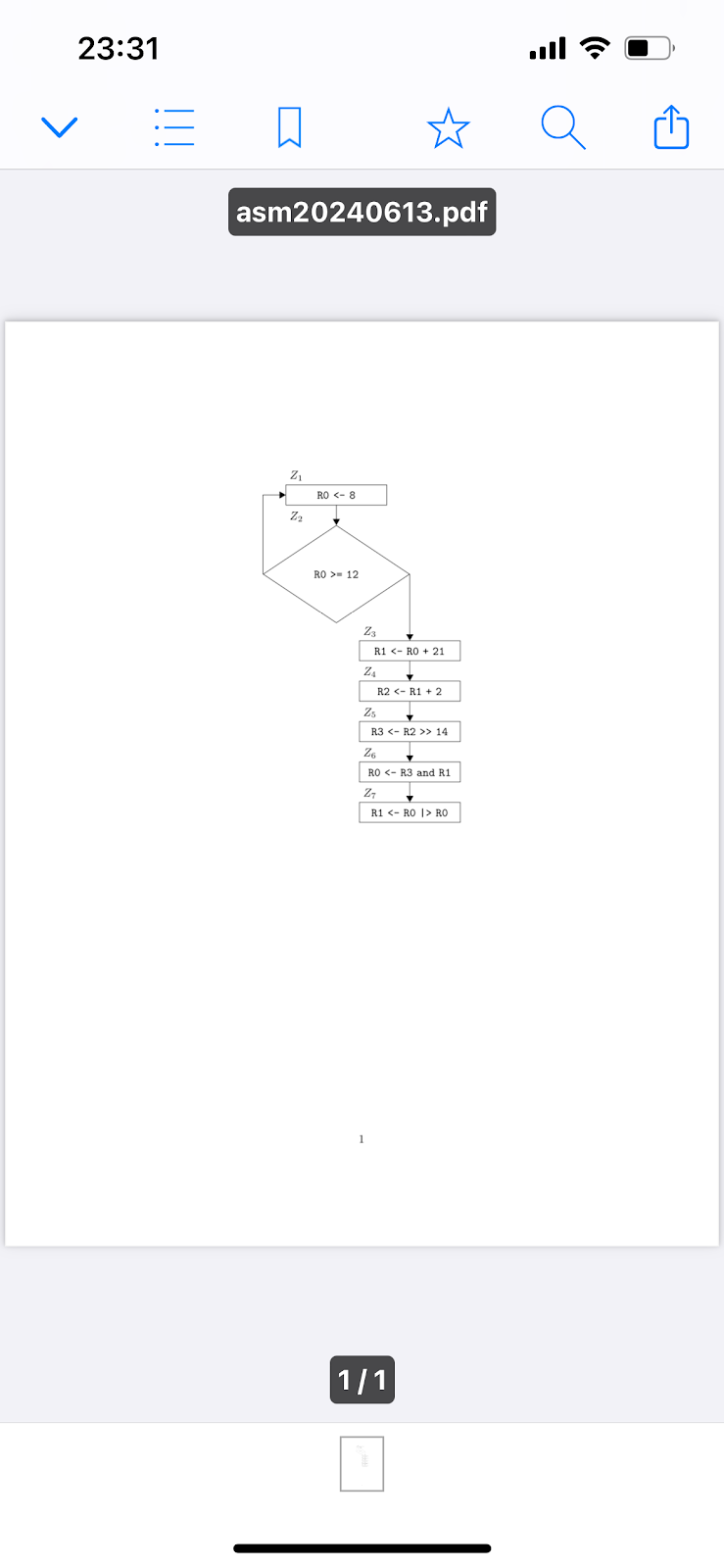

So, ich mache jetzt eine aufgabe mit quine mc cluskey.

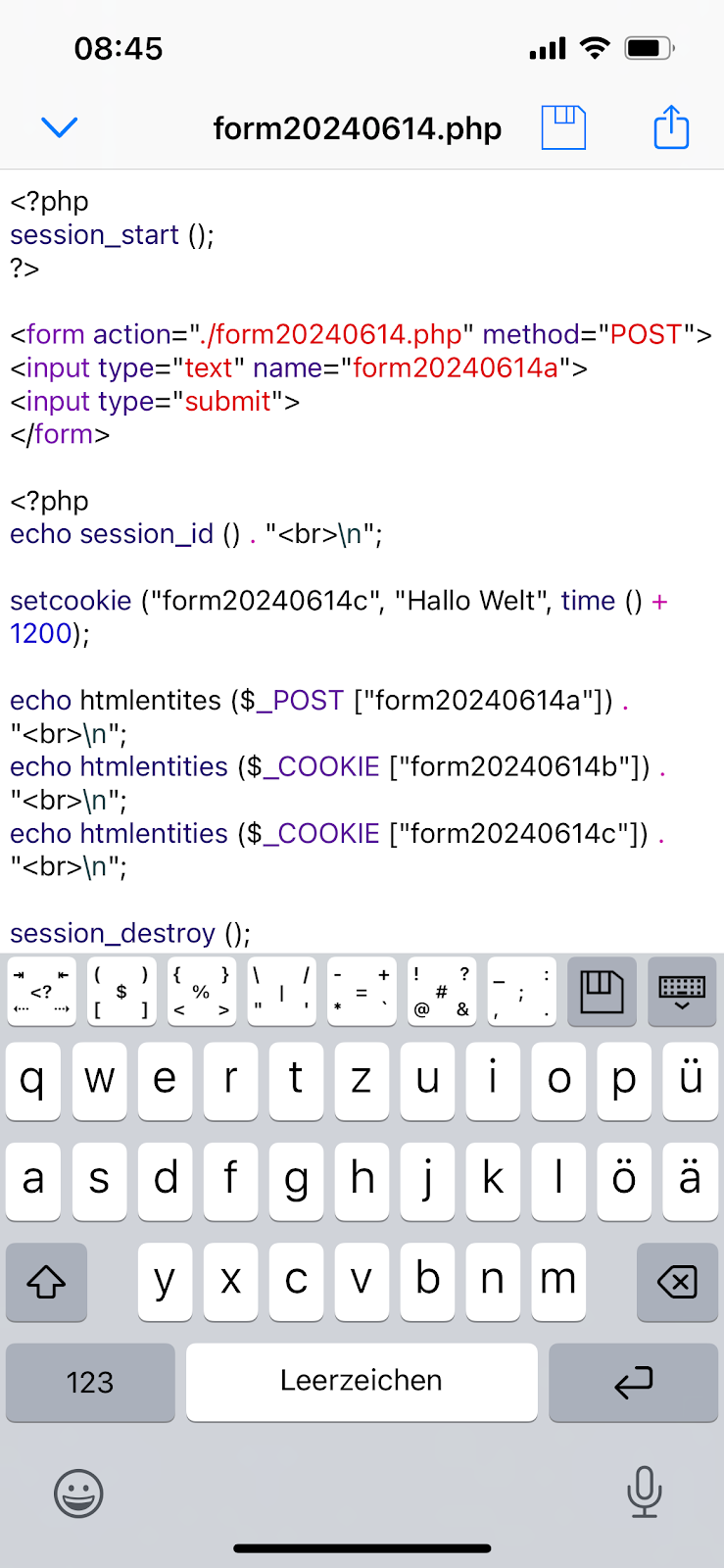

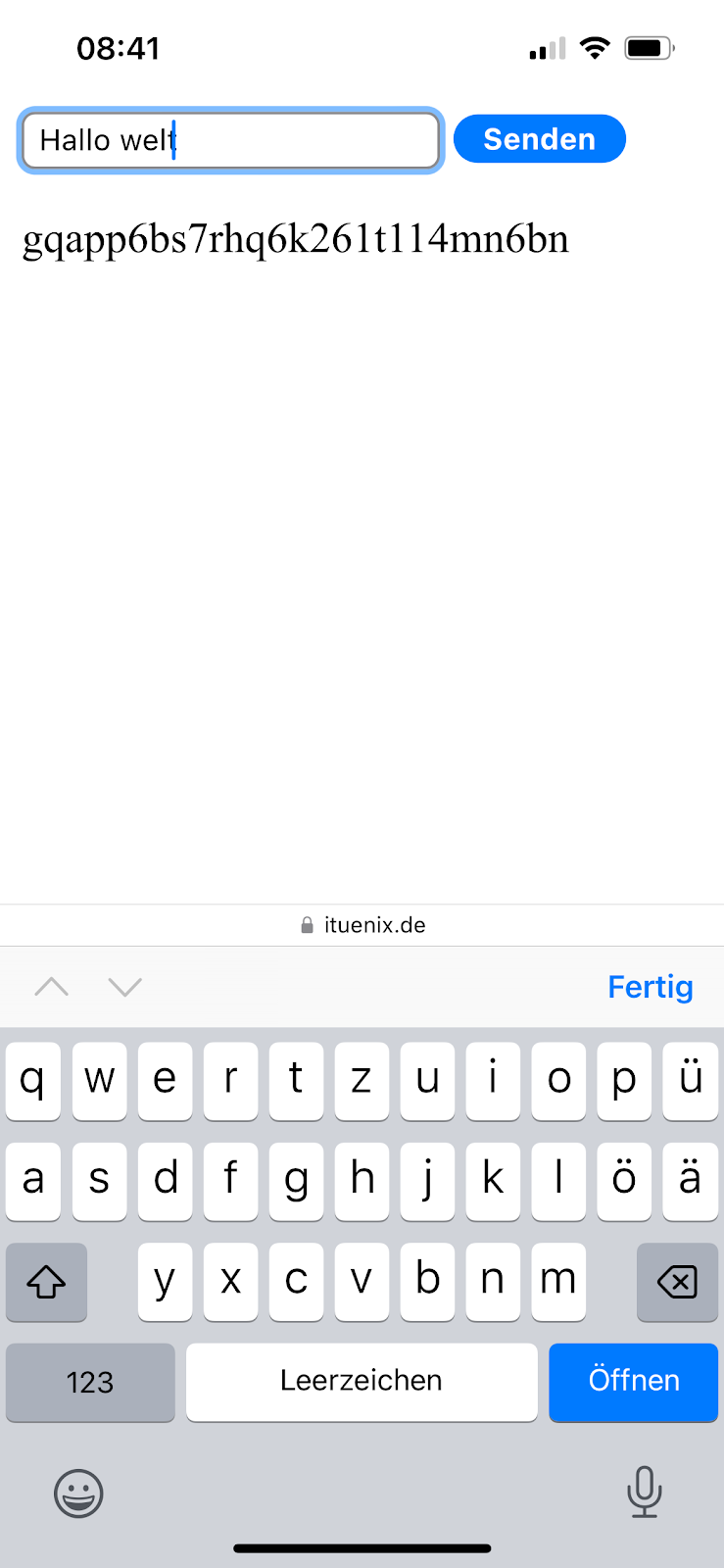

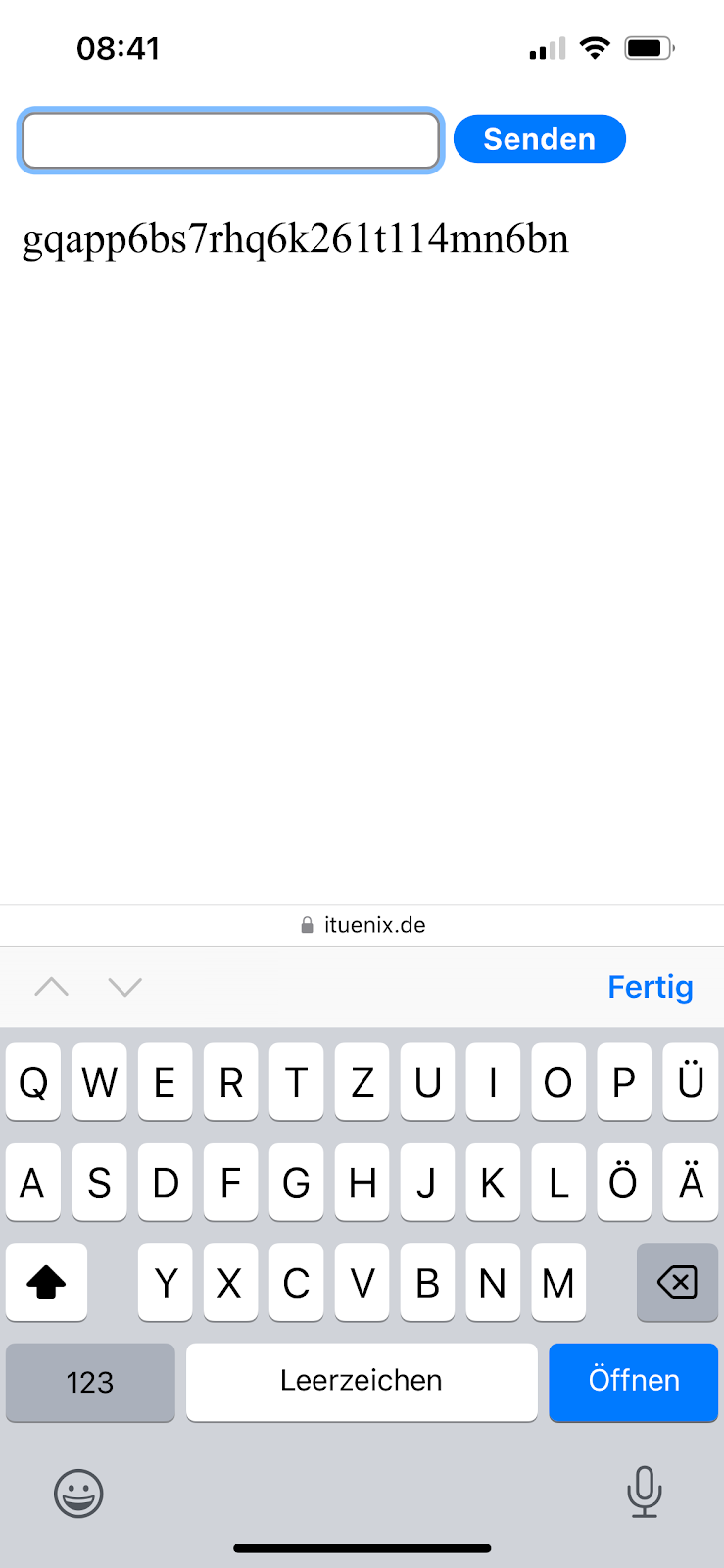

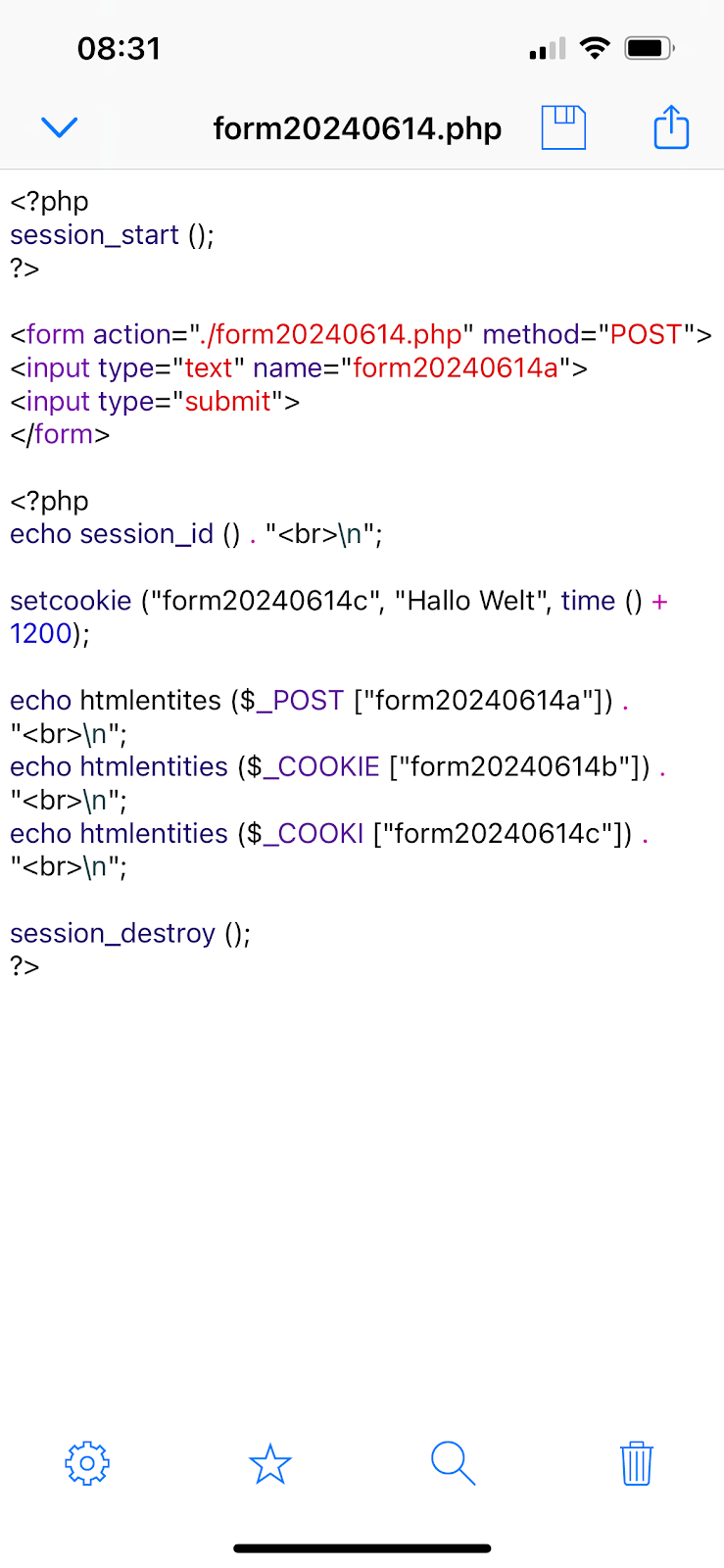

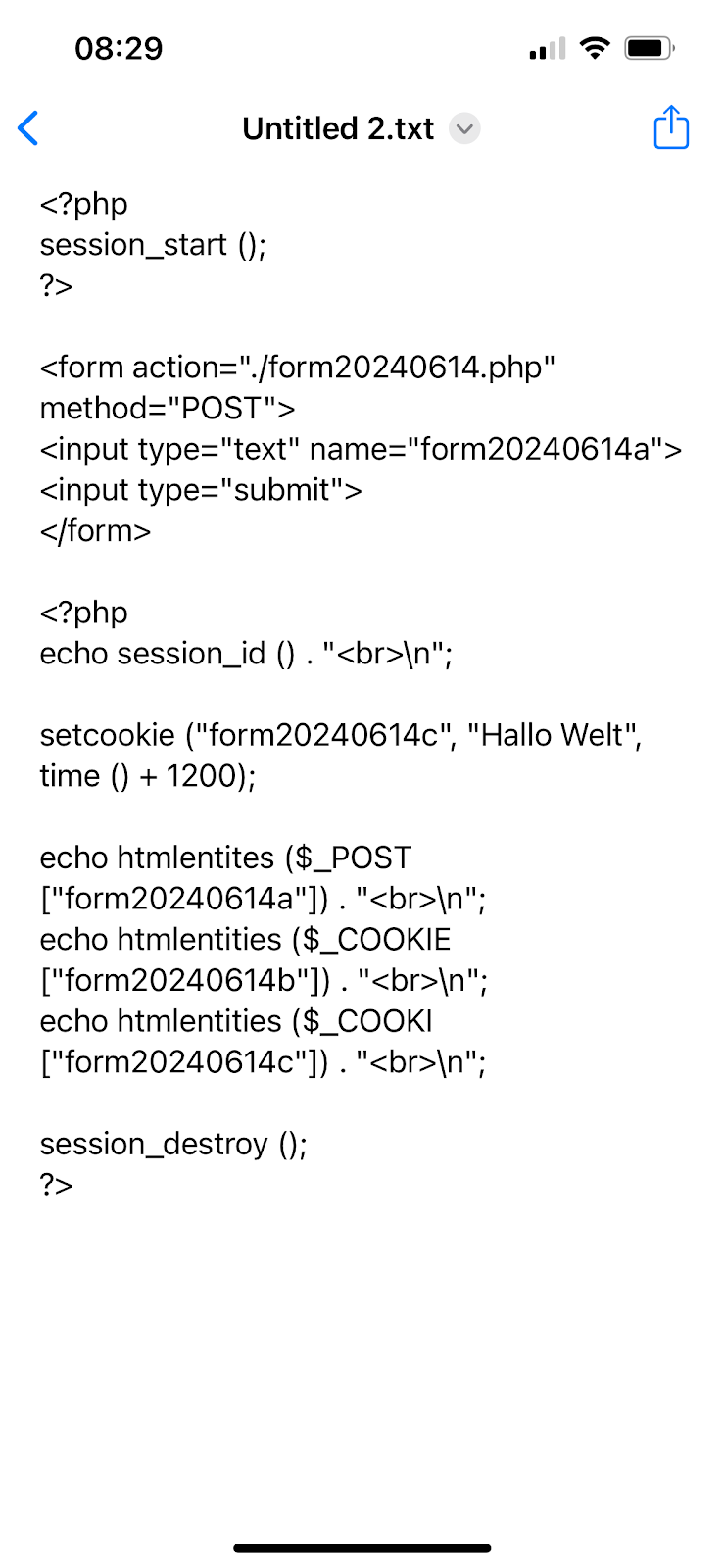

<?php

session_start ();

?>

<!-- https://phpbb3.ituenix.de/viewtopic.php?p=2504\&sid=fe31b12ff2b3b374eaca692913acc42d#p2504 -->

<form action="./form20240614.php" method="POST">

<input type="text" name="form20240614a">

<input type="submit">

</form>

<?php

echo session_id () . "<br>n";

setcookie ("form20240614c", "Hallo Welt", time () + 1200);

echo htmlentites (\$_POST ["form20240614a"]) . "<br>n";

echo htmlentities (\$_COOKIE ["form20240614b"]) . "<br>n";

echo htmlentities (\$_COOKIE ["form20240614c"]) . "<br>n";

session_destroy ();

?>

<?php

session_start ();

?>

<!-- https://phpbb3.ituenix.de/viewtopic.php?p=2504\&sid=fe31b12ff2b3b374eaca692913acc42d#p2504 -->

<form action="./form20240614.php" method="POST">

<input type="text" name="form20240614a">

<input type="submit">

</form>

<?php

echo session_id () . "<br>n";

setcookie ("form20240614c", "Hallo Welt", time () + 1200);

echo htmlentites (\$_POST ["form20240614a"]) . "<br>n";

echo htmlentities (\$_COOKIE ["form20240614b"]) . "<br>n";

echo htmlentities (\$_COOKI ["form20240614c"]) . "<br>n";

session_destroy ();

?>

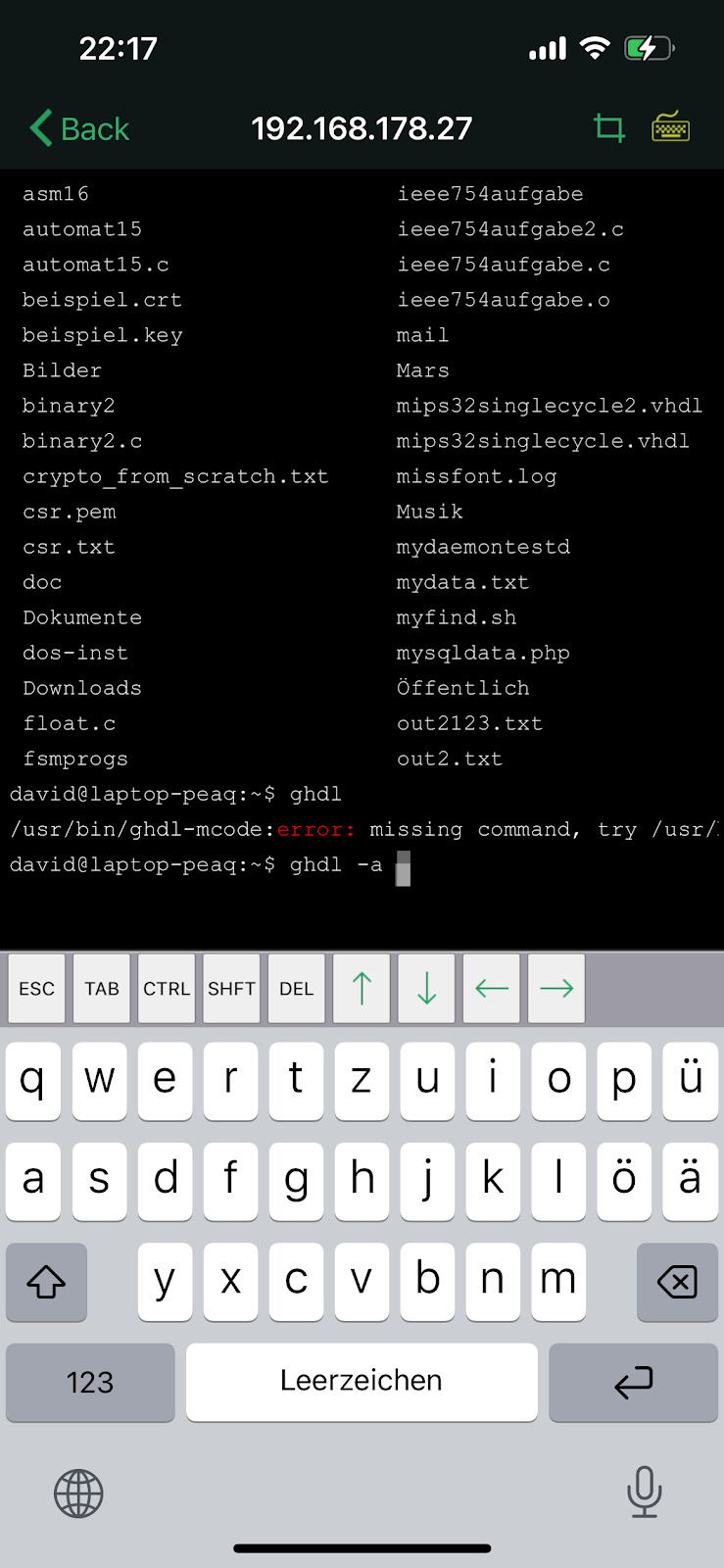

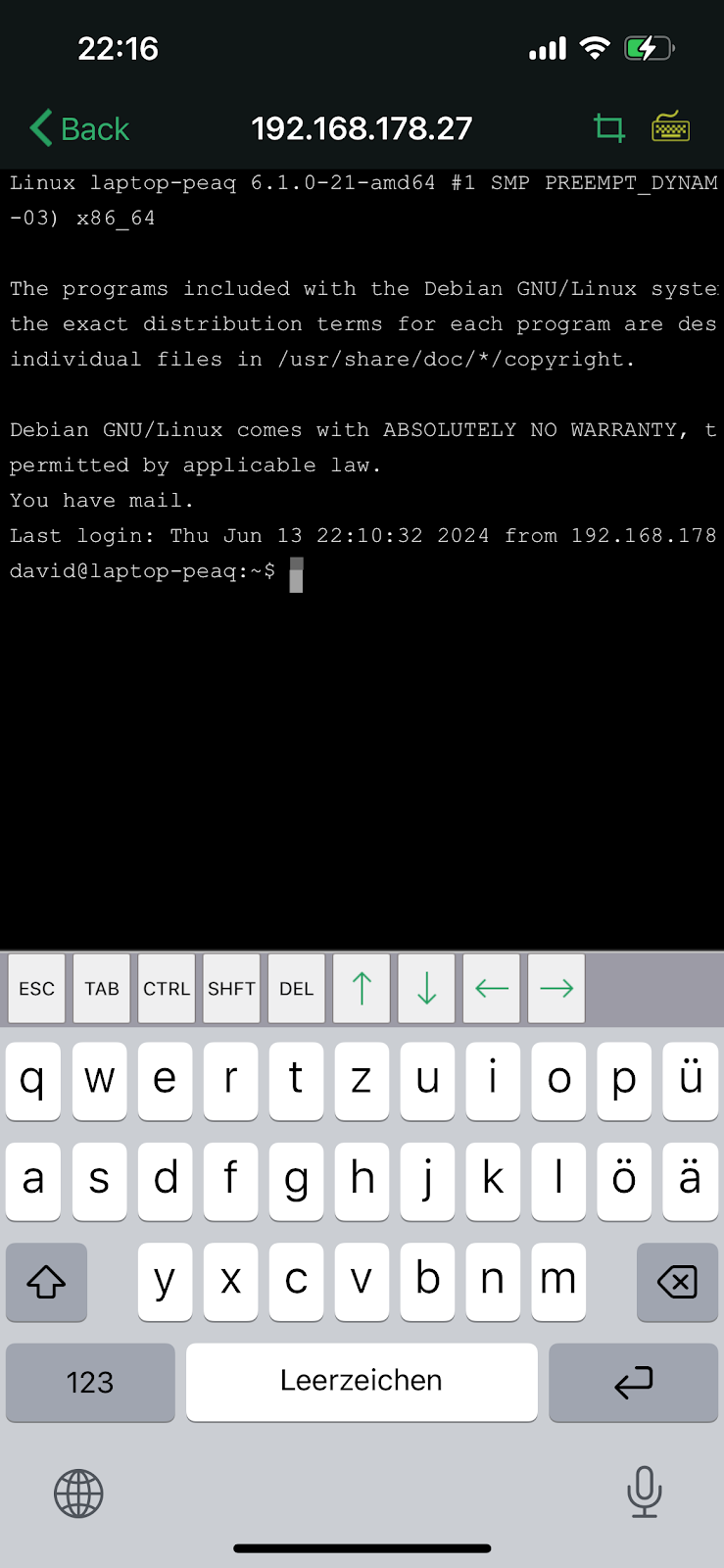

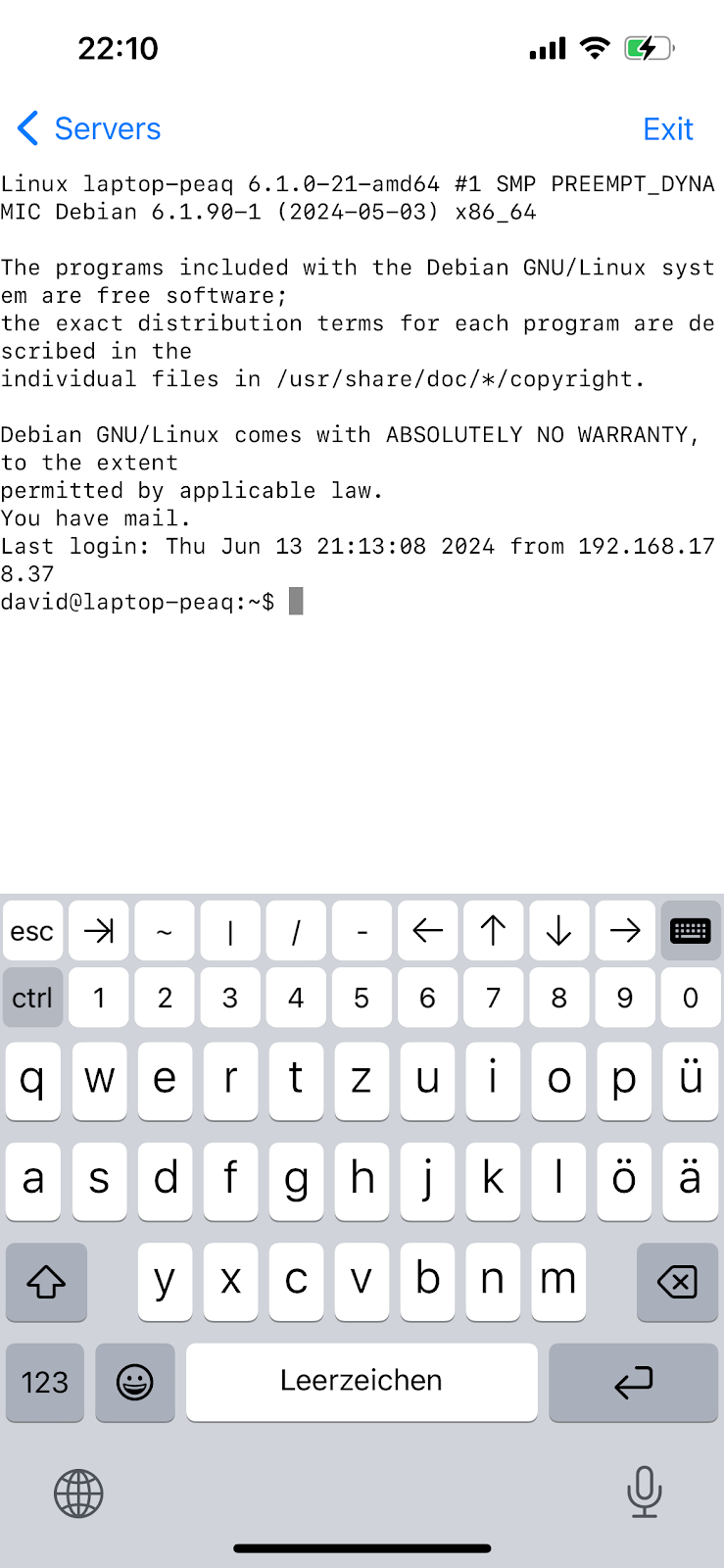

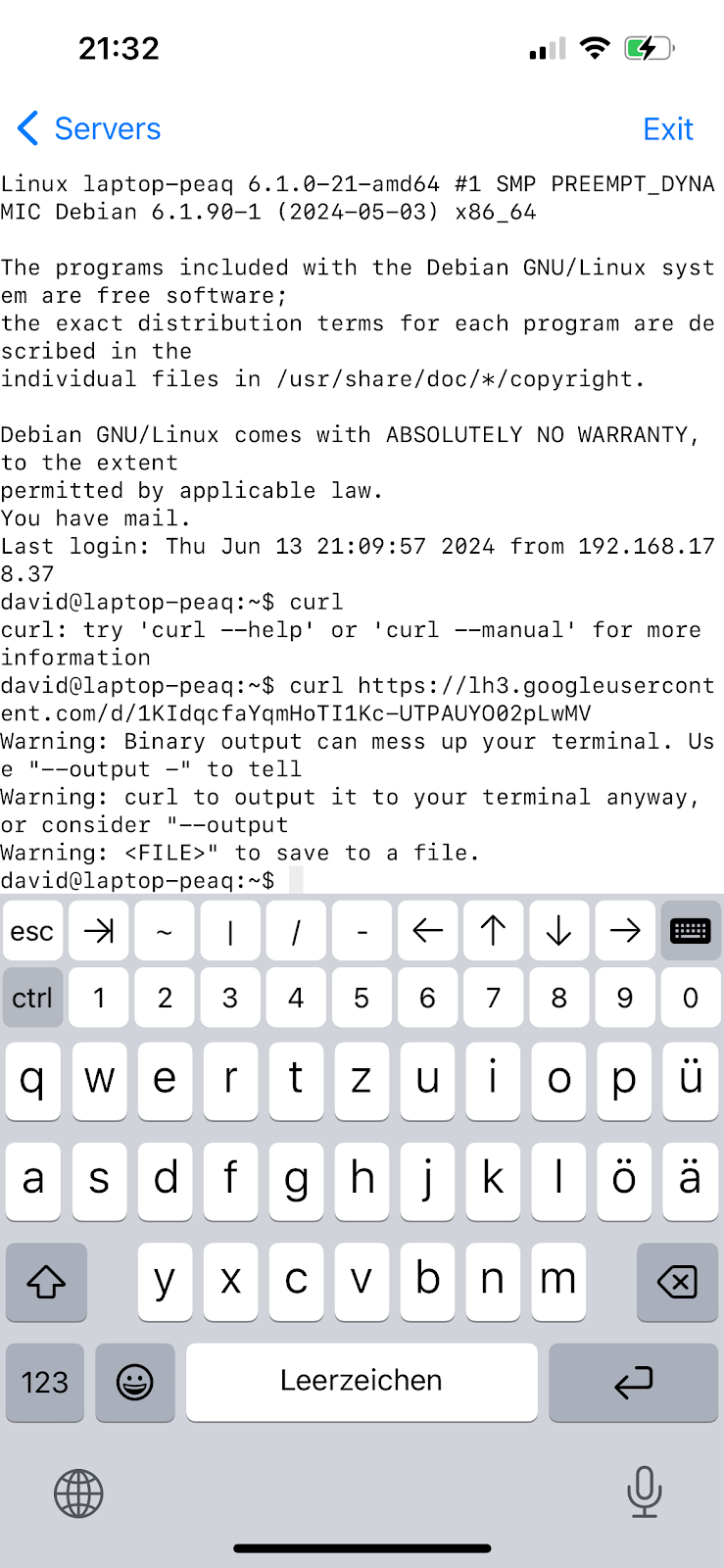

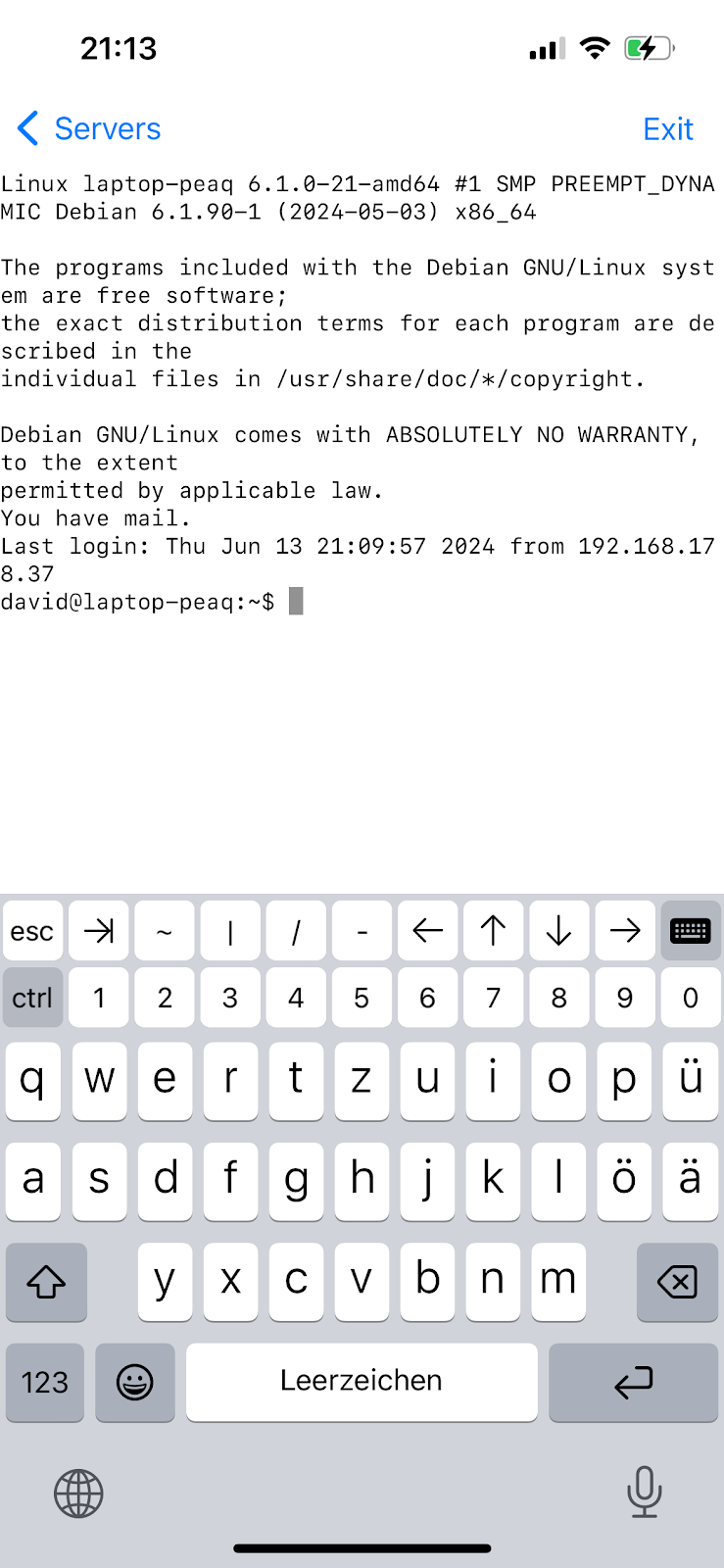

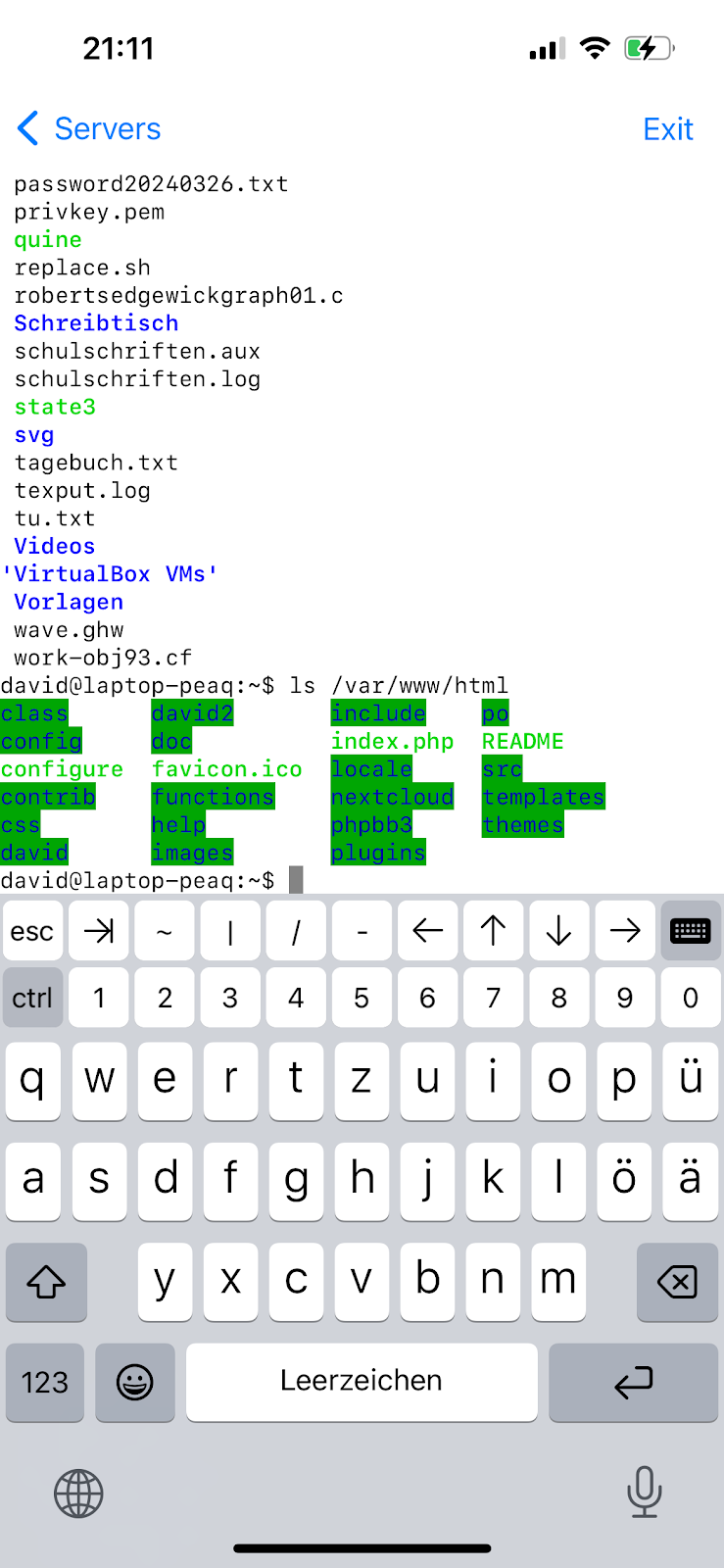

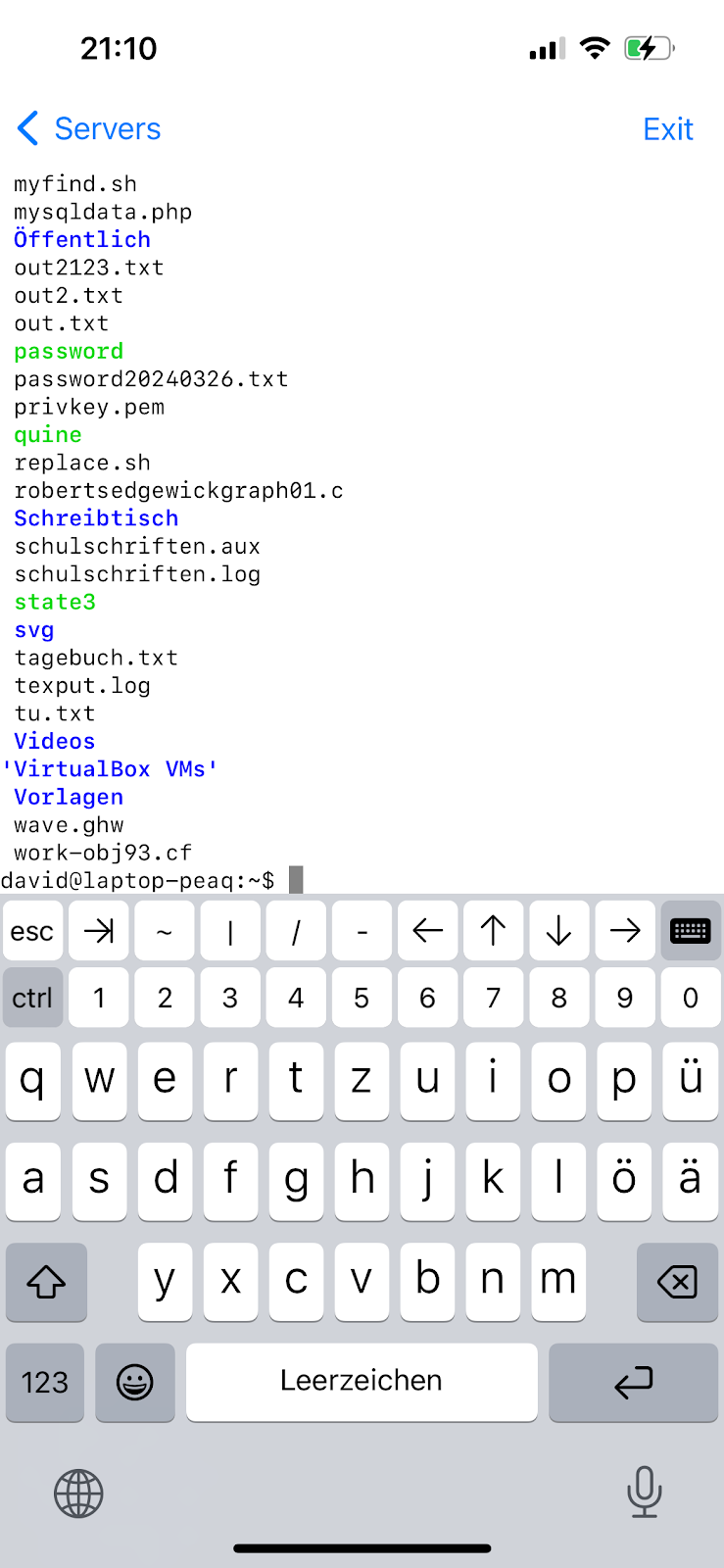

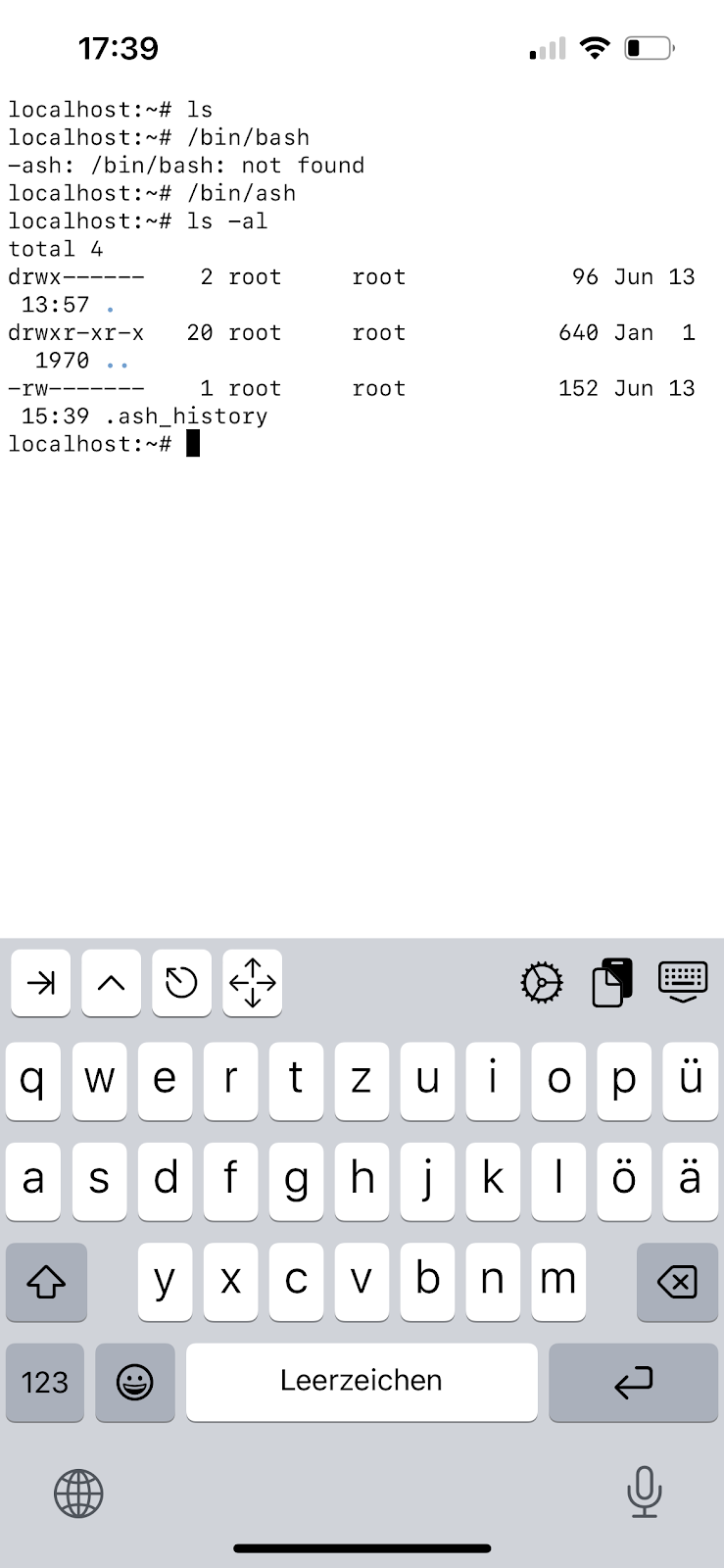

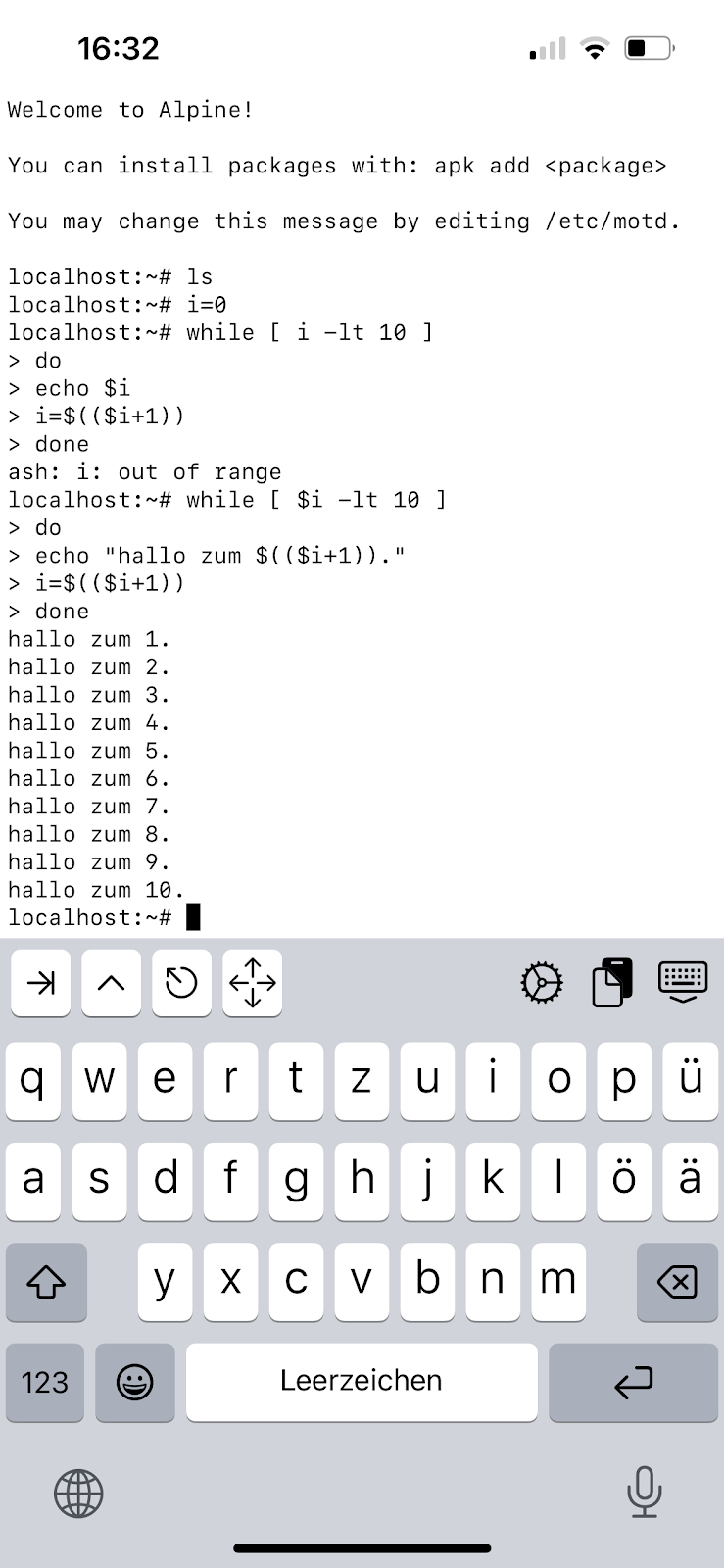

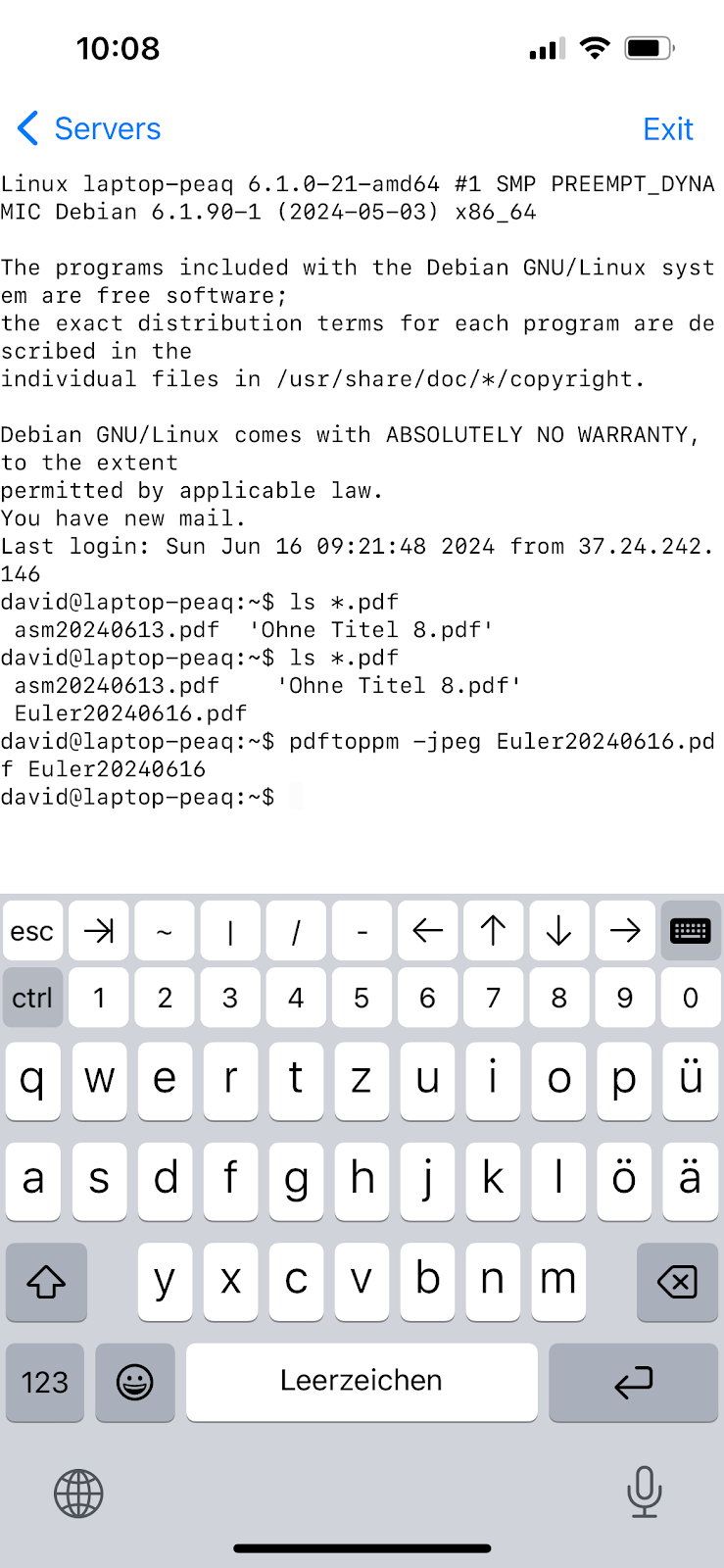

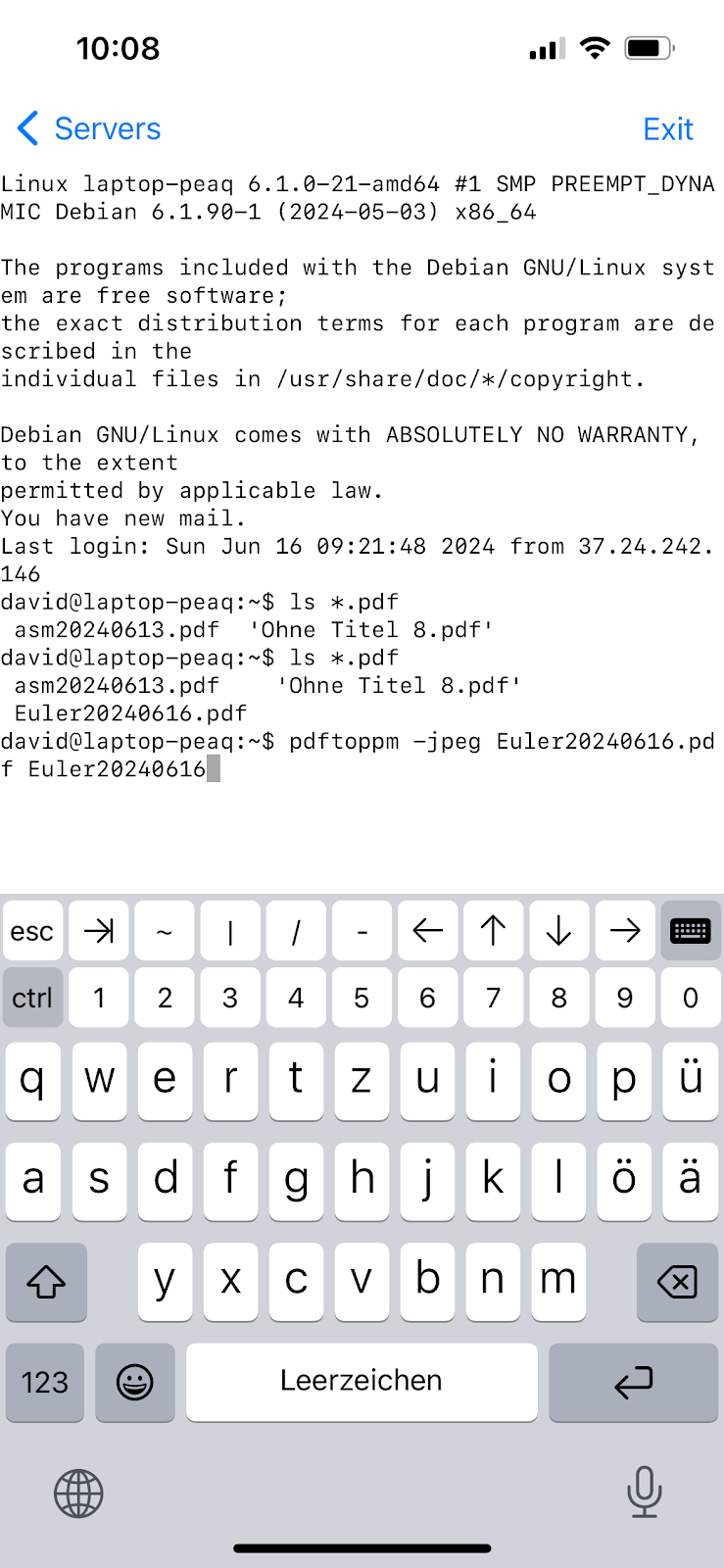

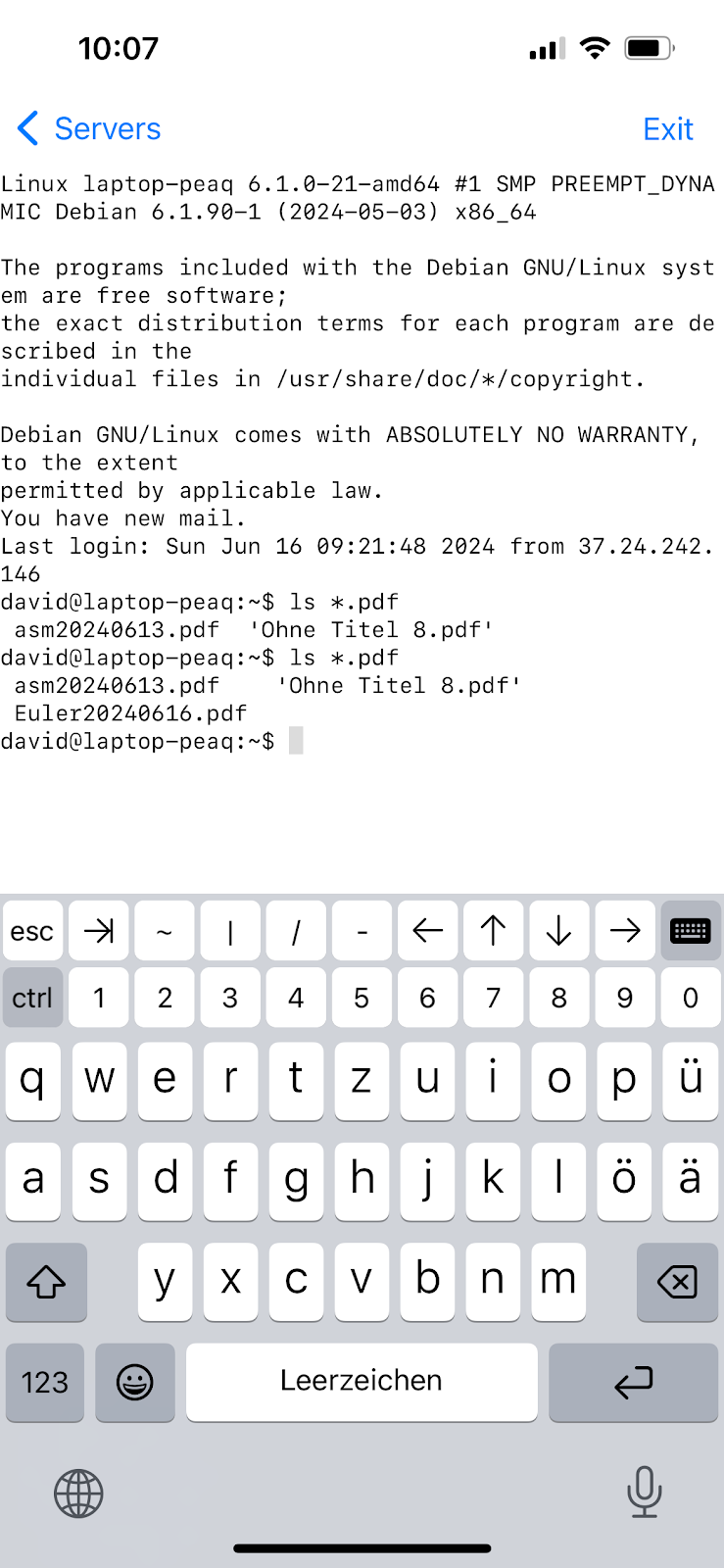

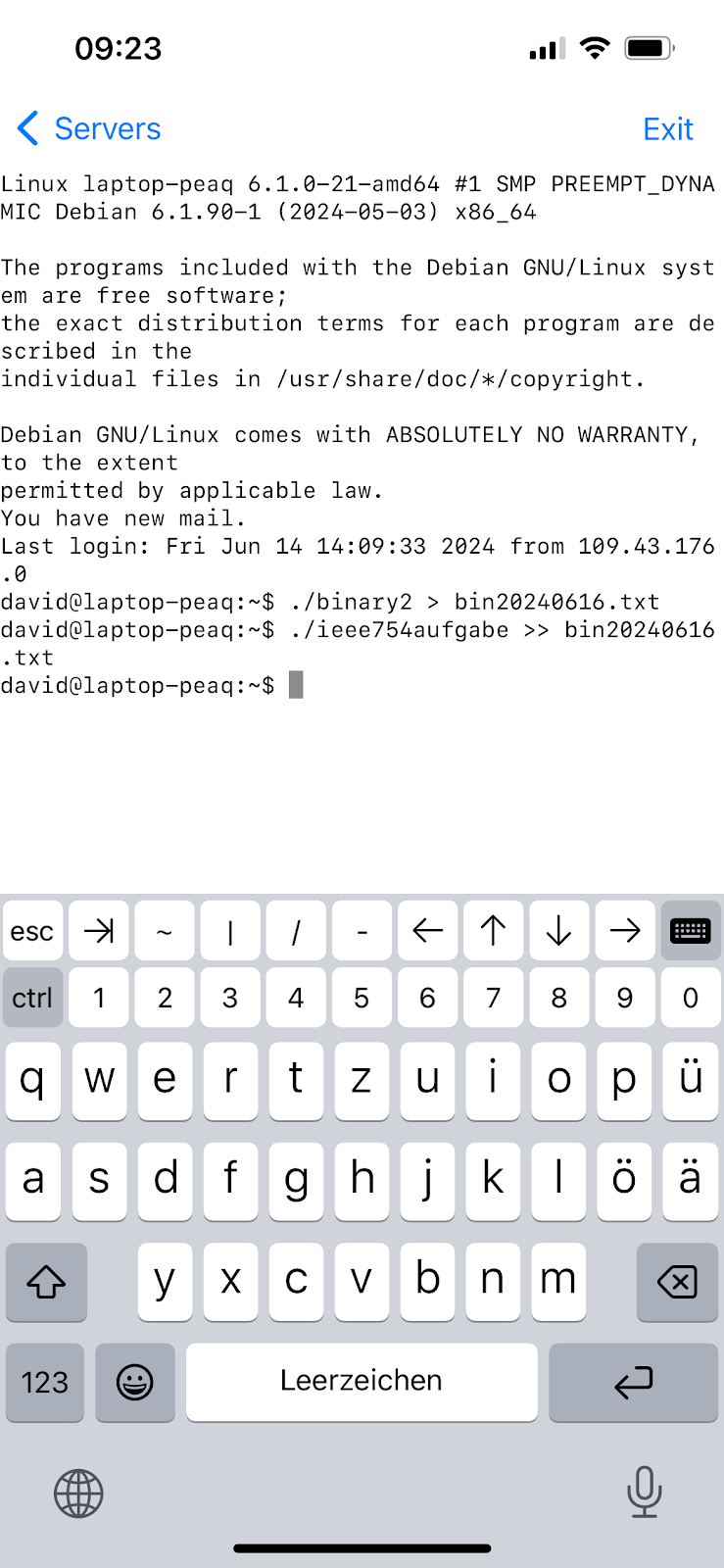

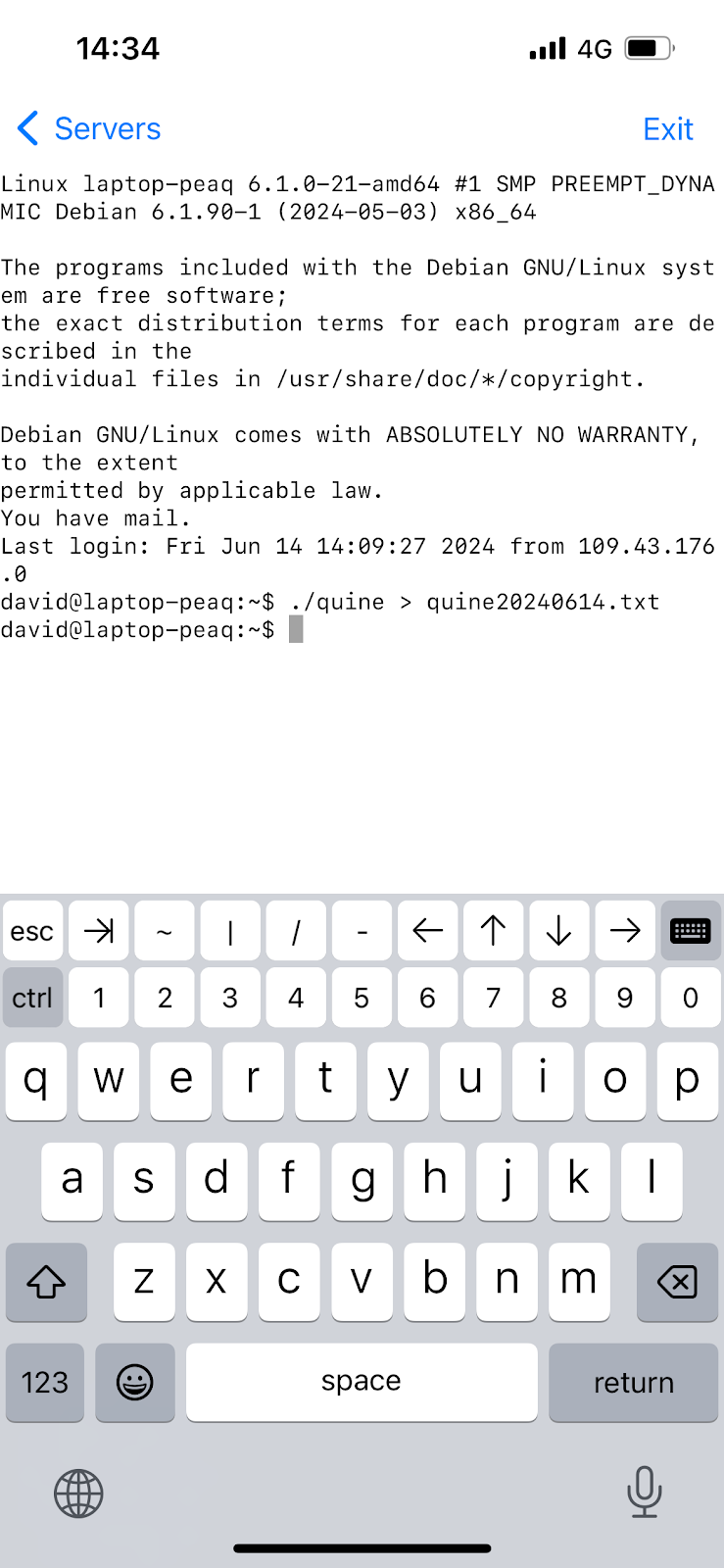

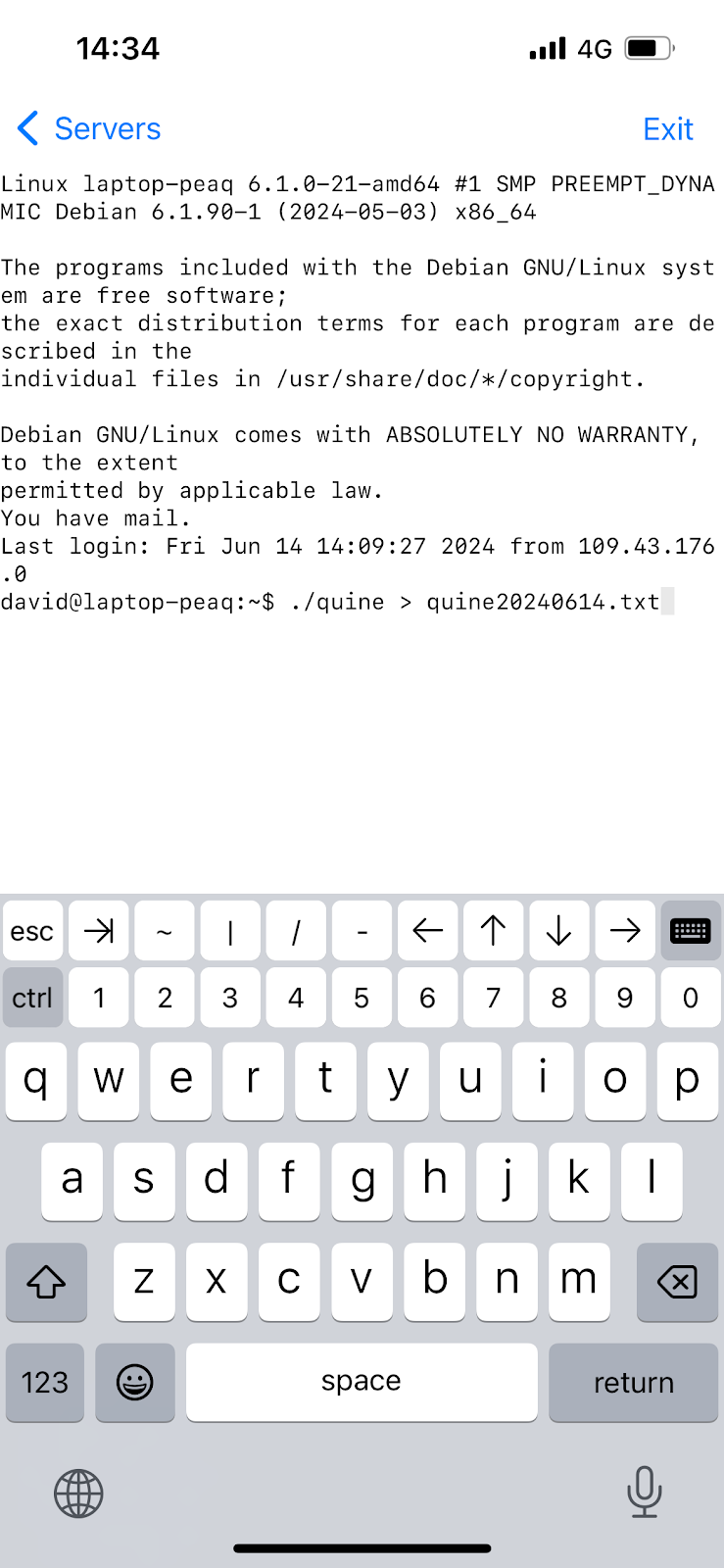

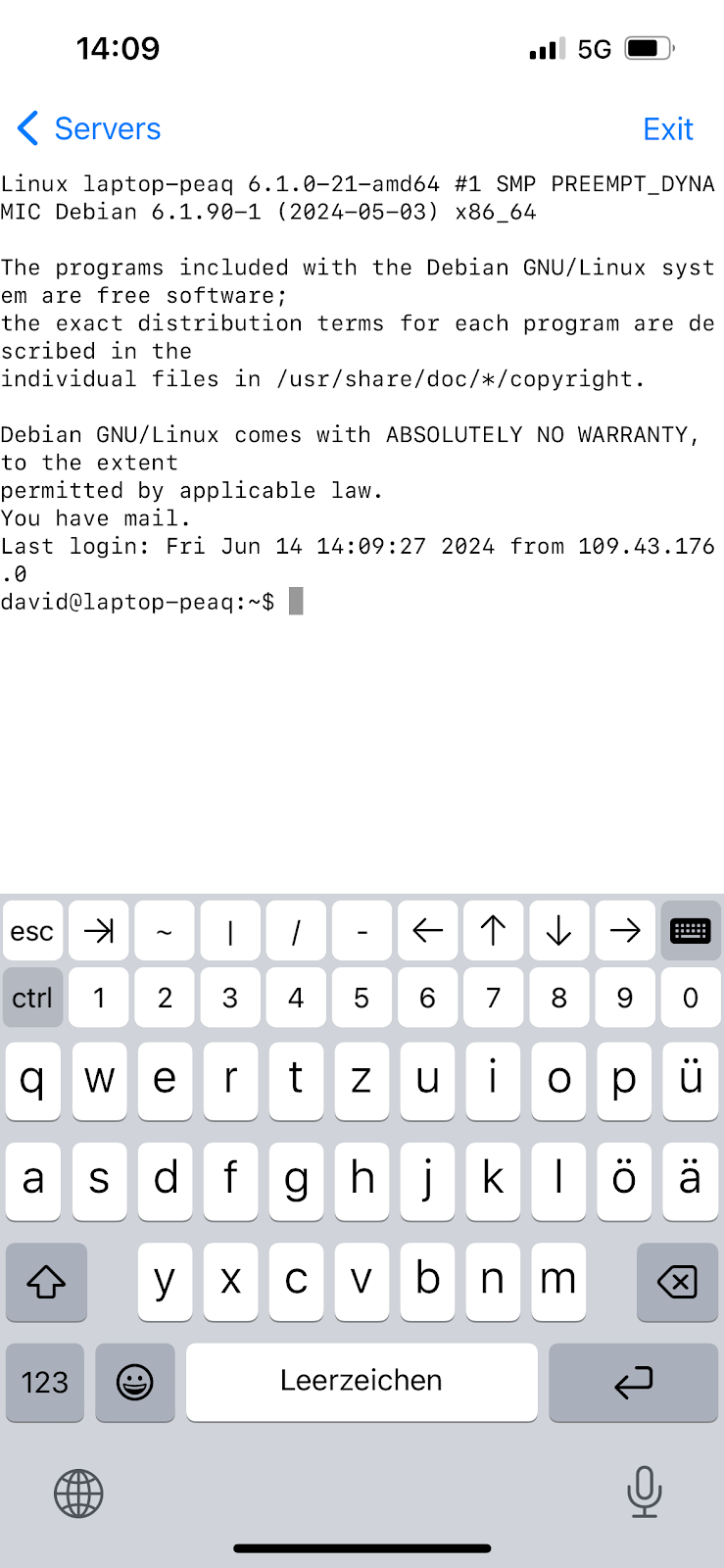

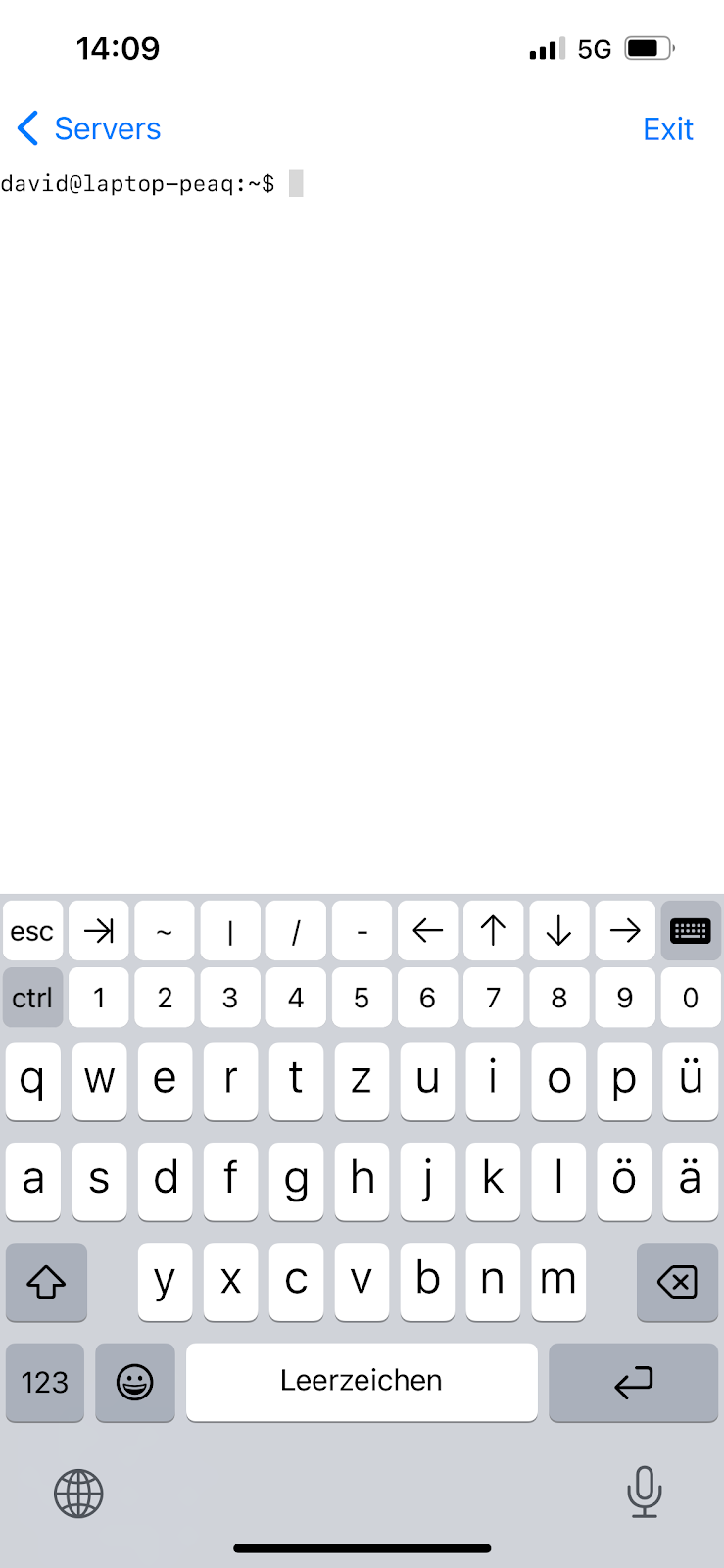

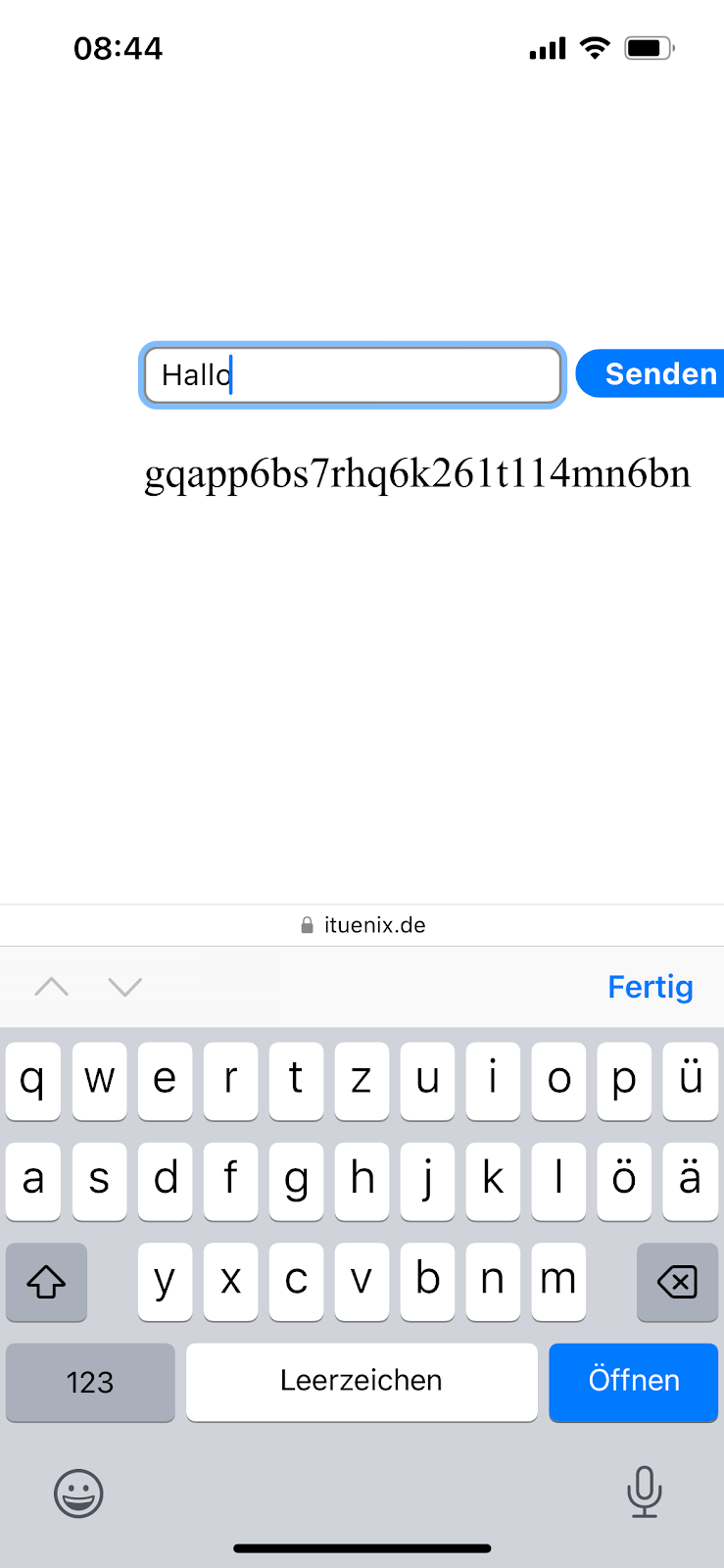

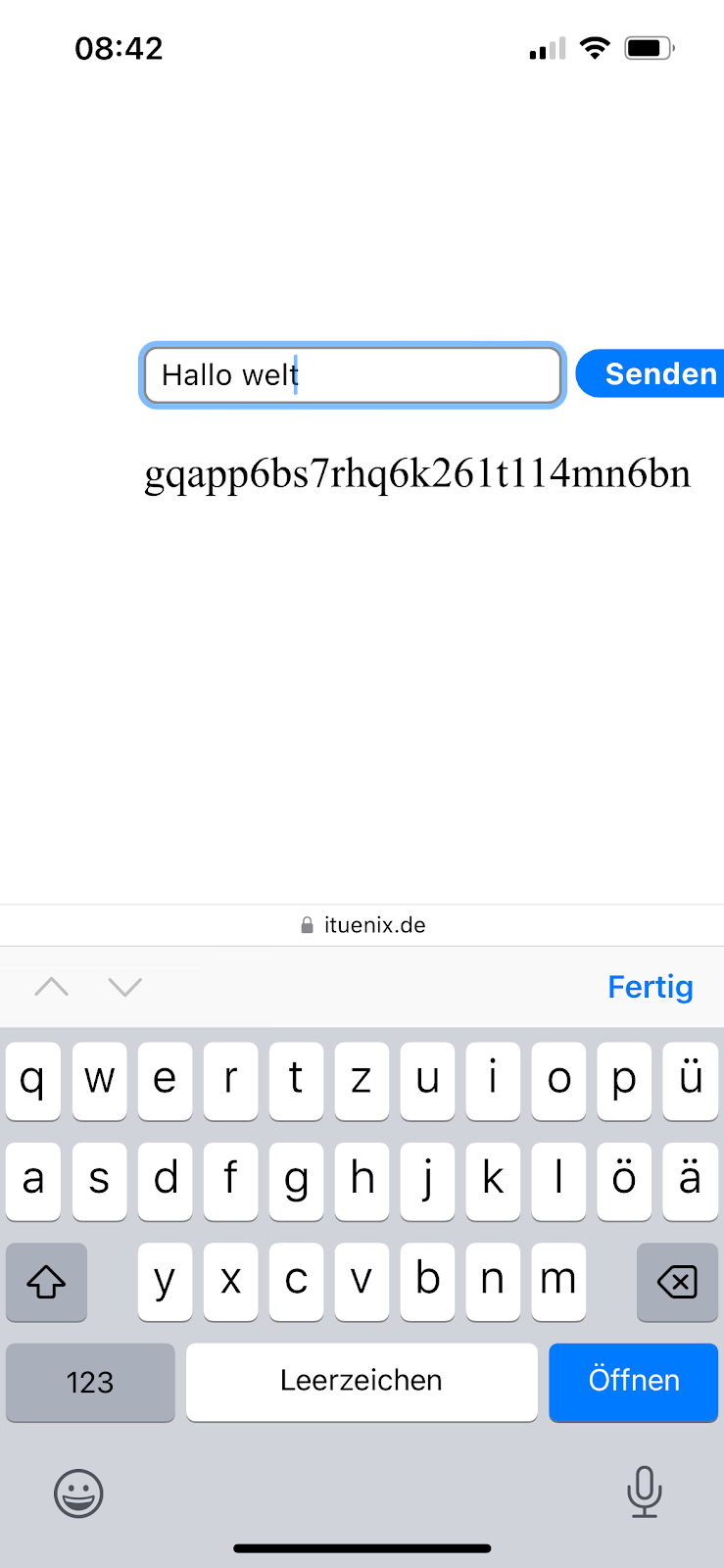

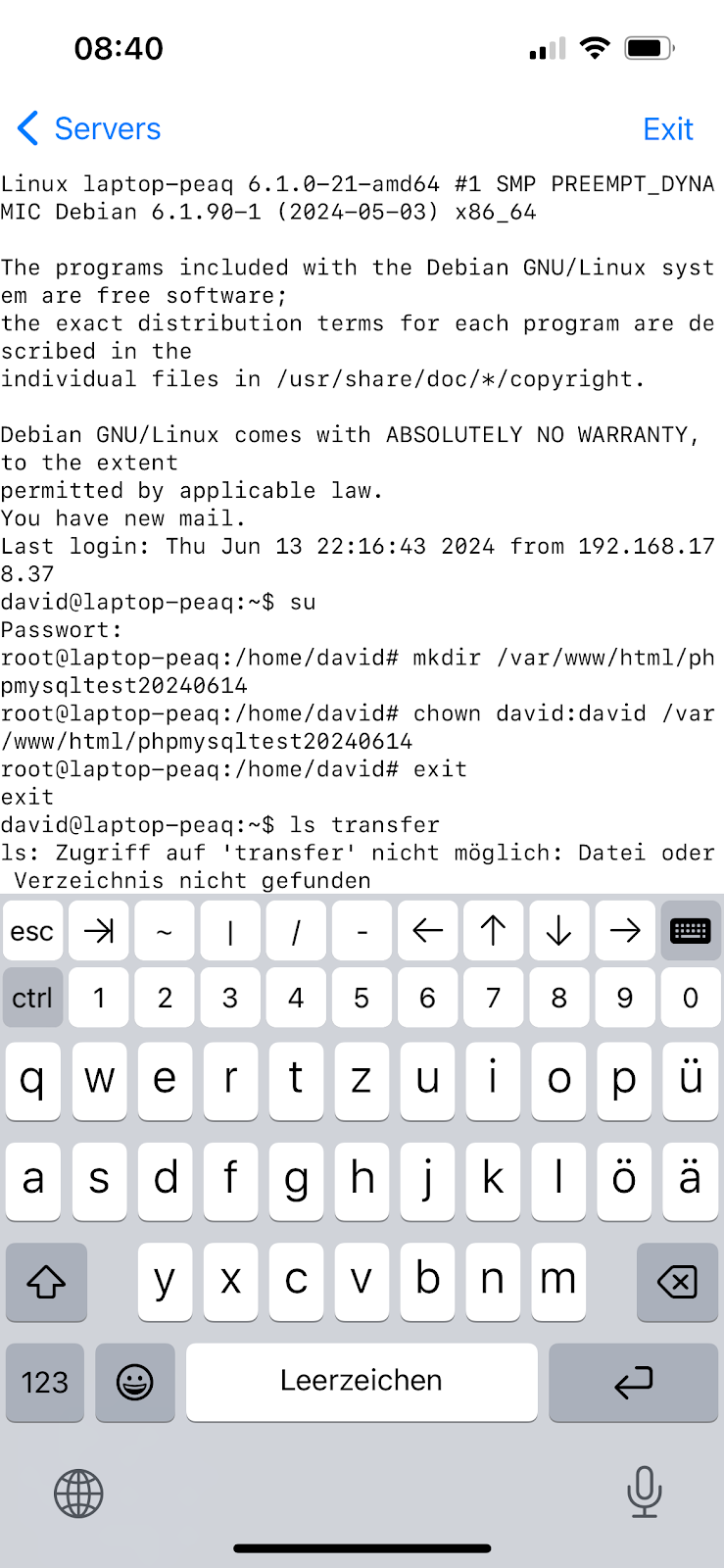

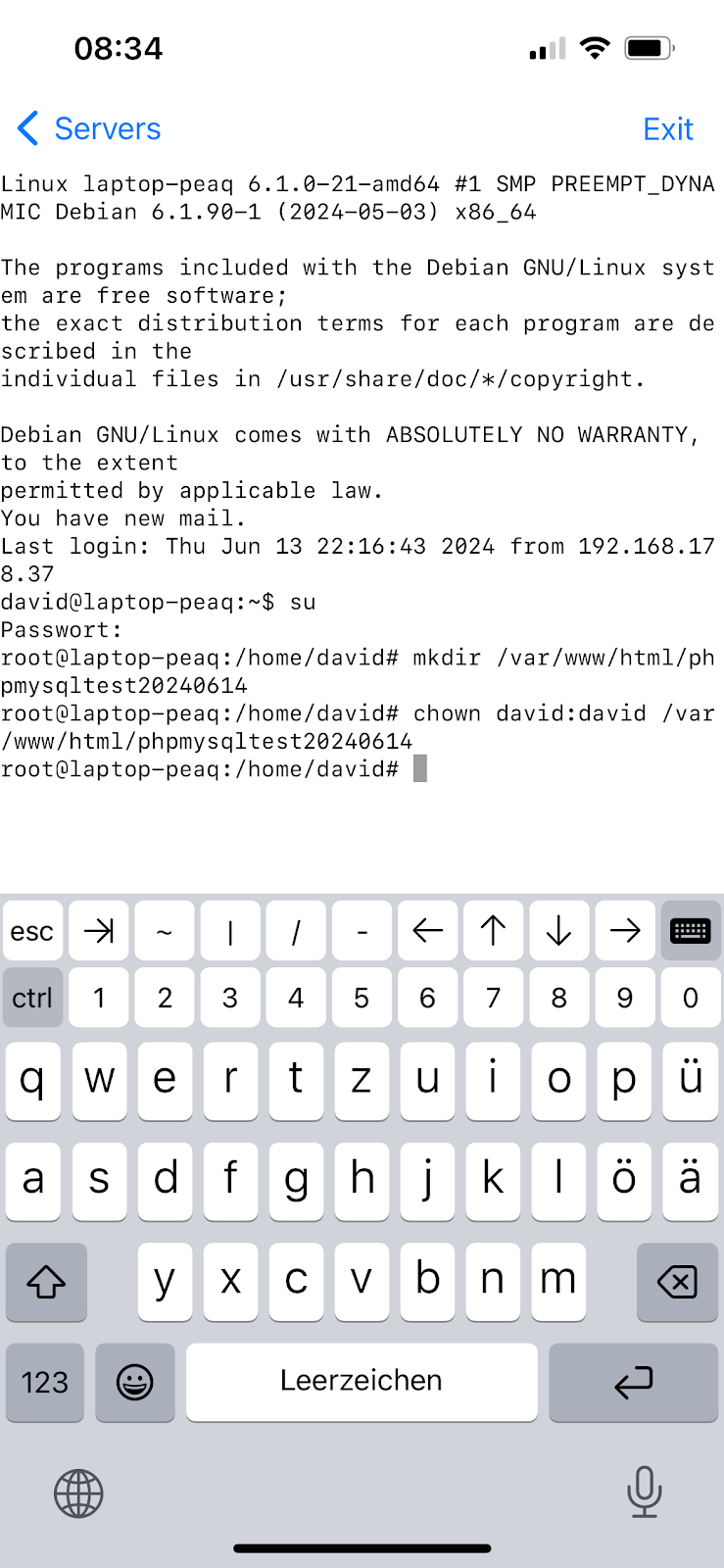

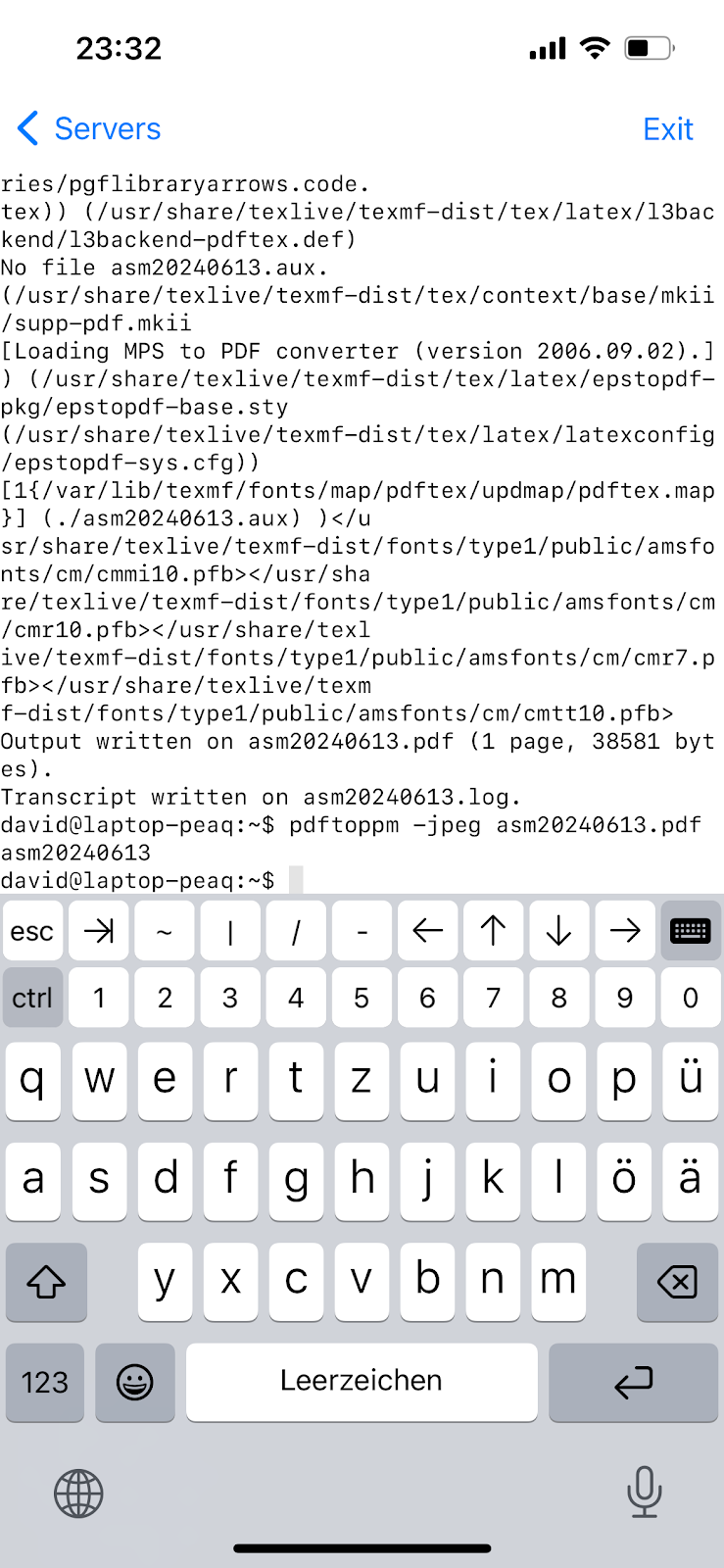

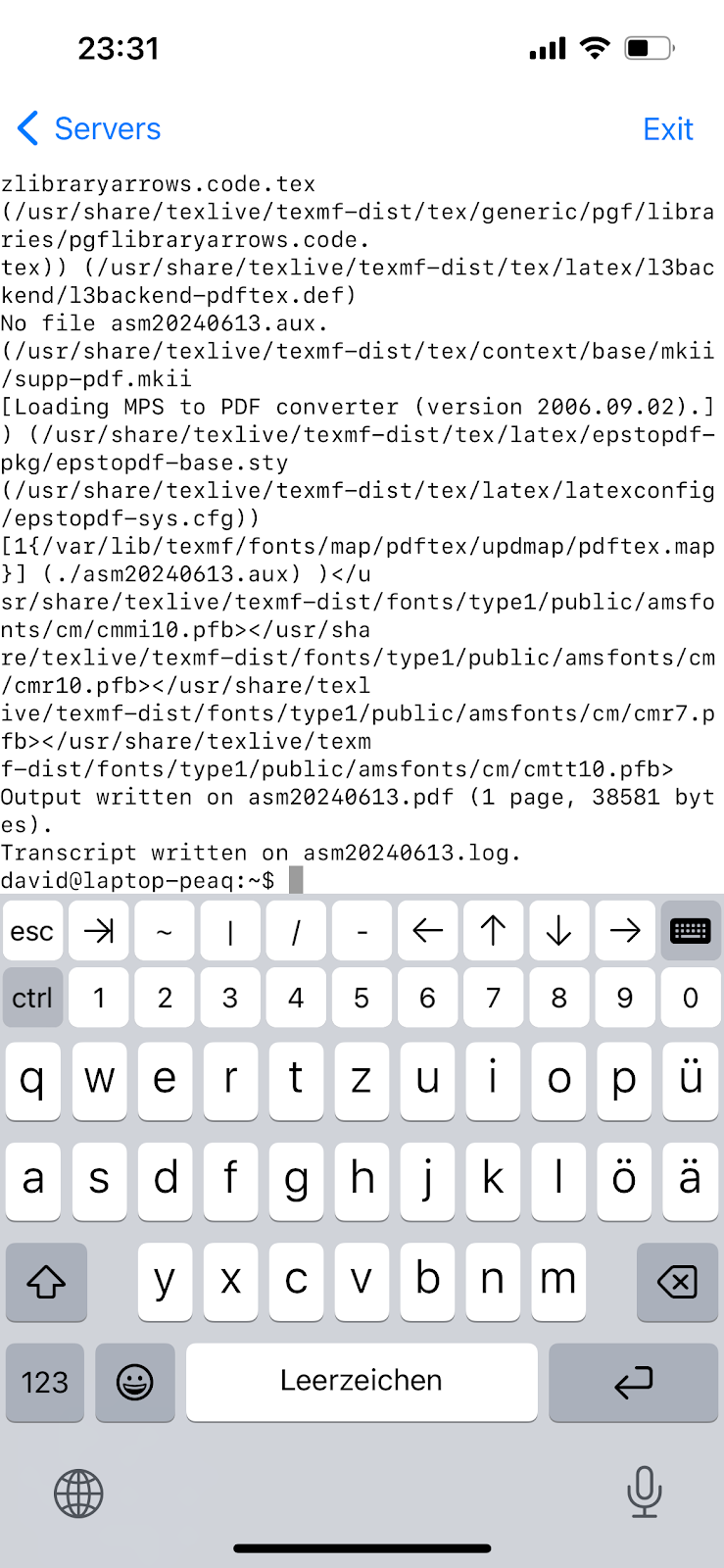

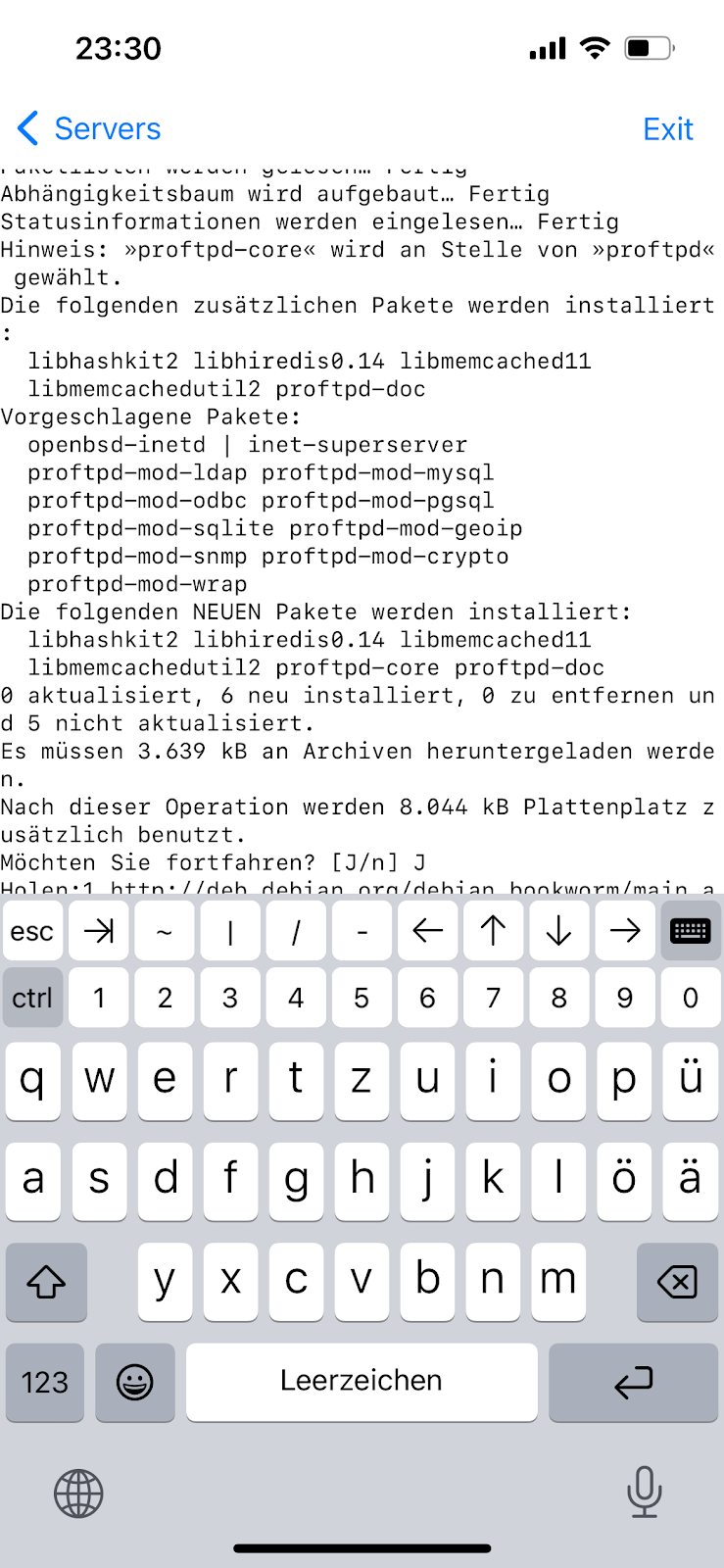

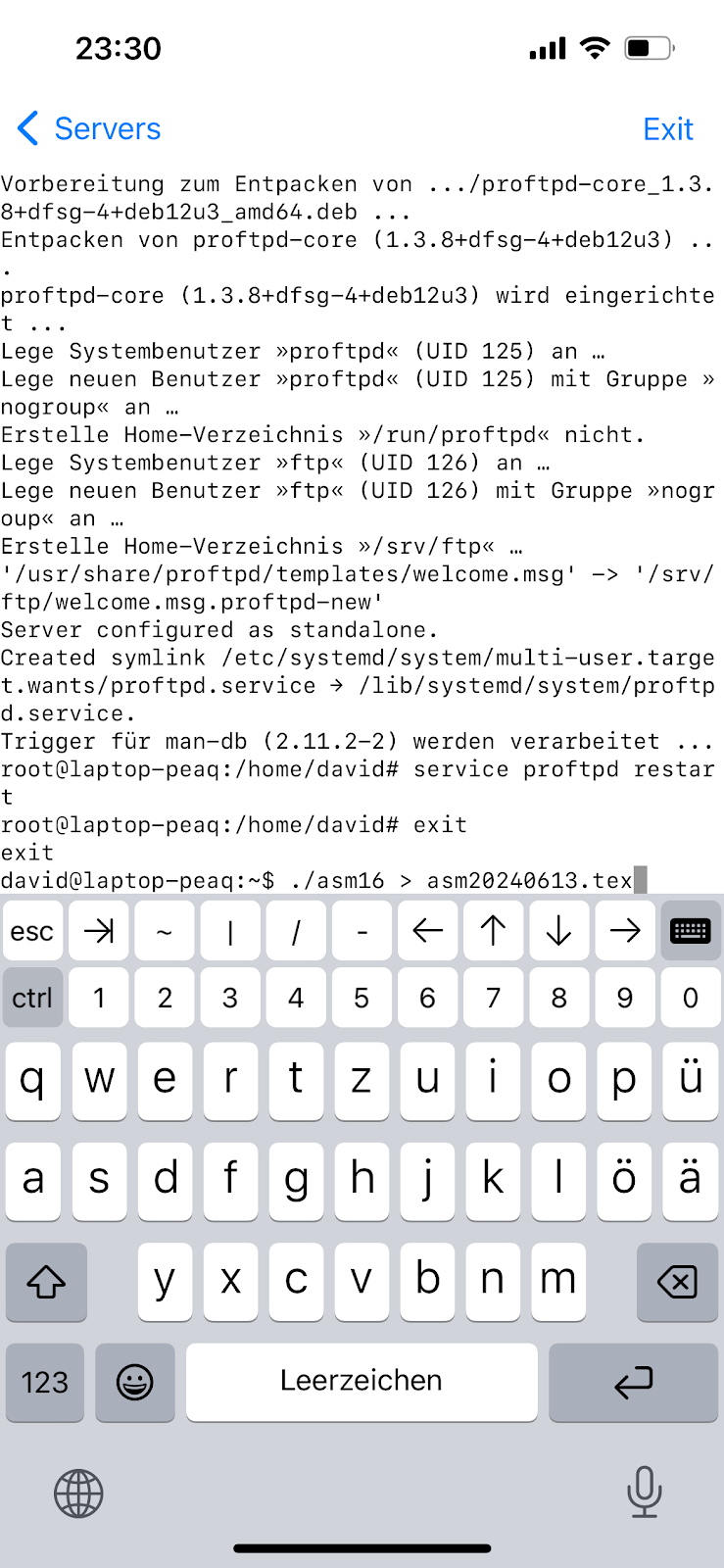

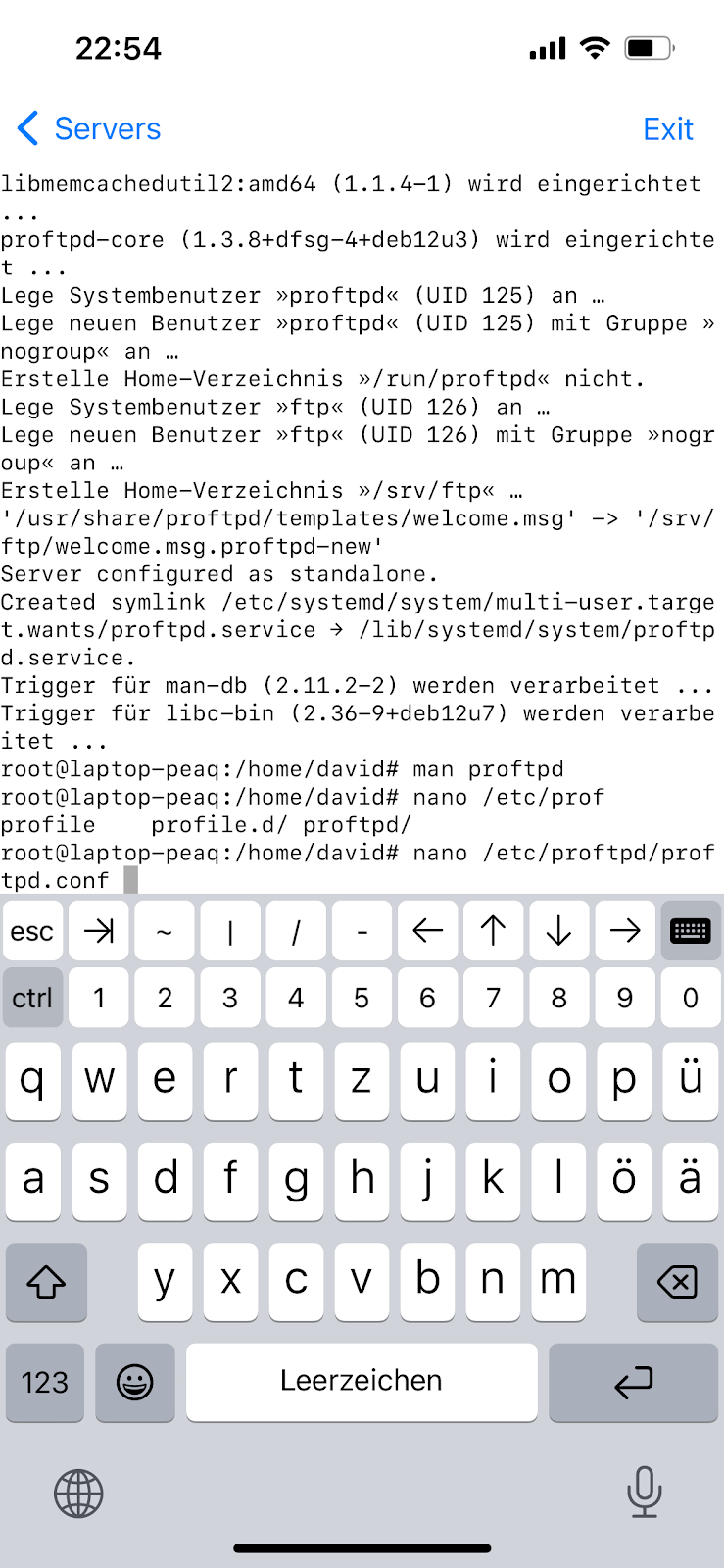

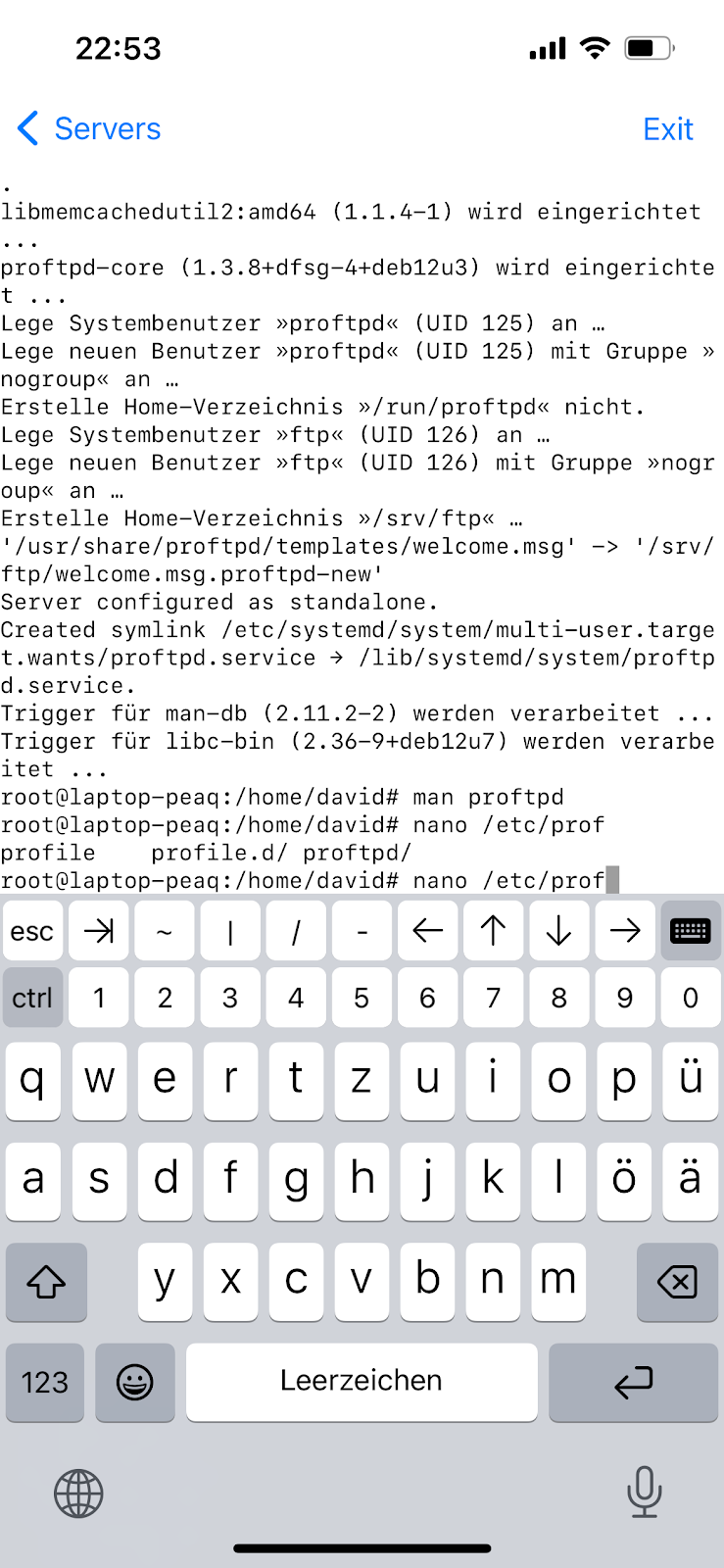

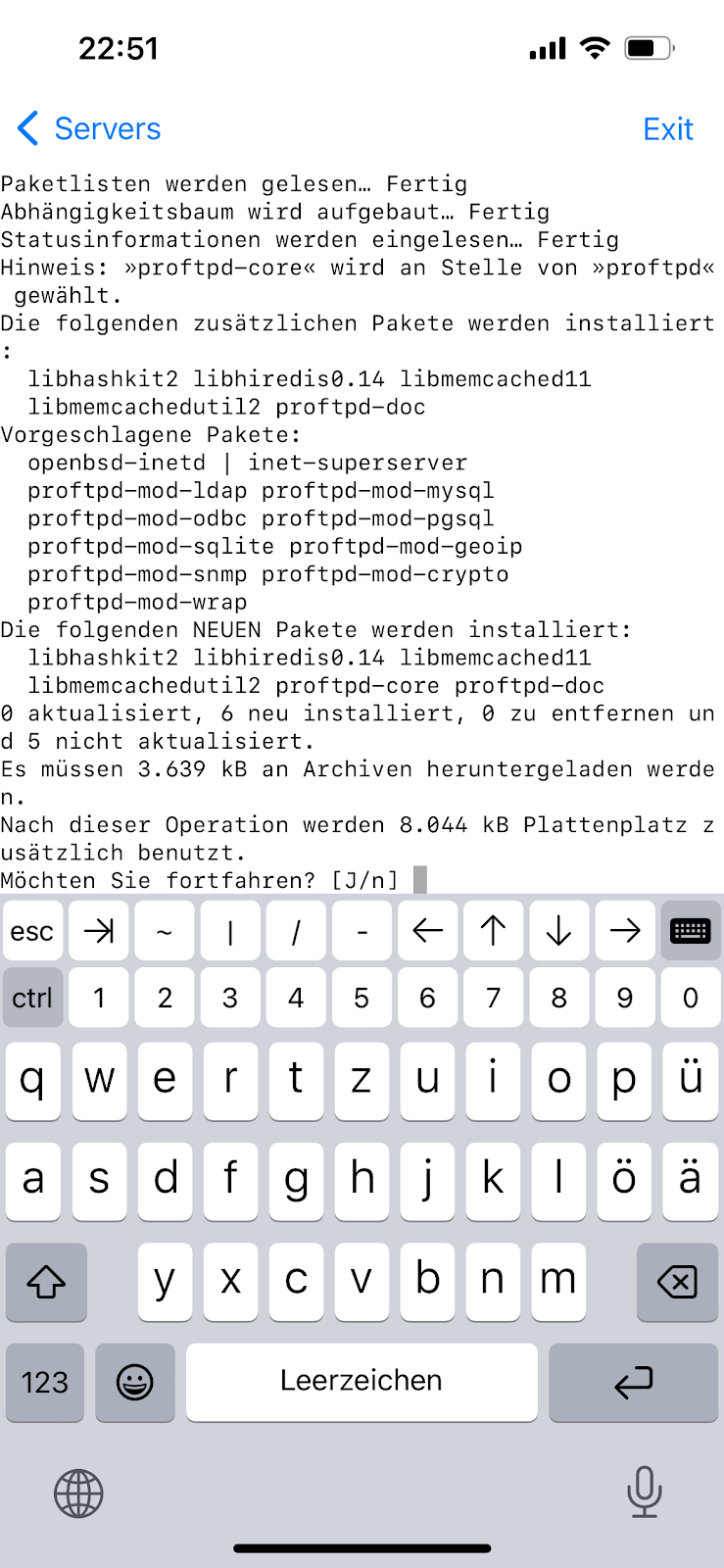

So, ich mache jetzt die ueblichen Aufgaben. Auf dem Linux Server aber dies mal vom Apple iPhone als sichtgeraet aus.

Ich fange heute auch mit dem mips32 an, jeden Tag ein bisschen, sonst aendert sich nichts

Ich erstelle gleich mal eine UEbungs pdf wie ueblich und zeige es geht.

Ich gebe das jetzt auf der Firewall frei und hoffe, ich komme aus dem Internet rein

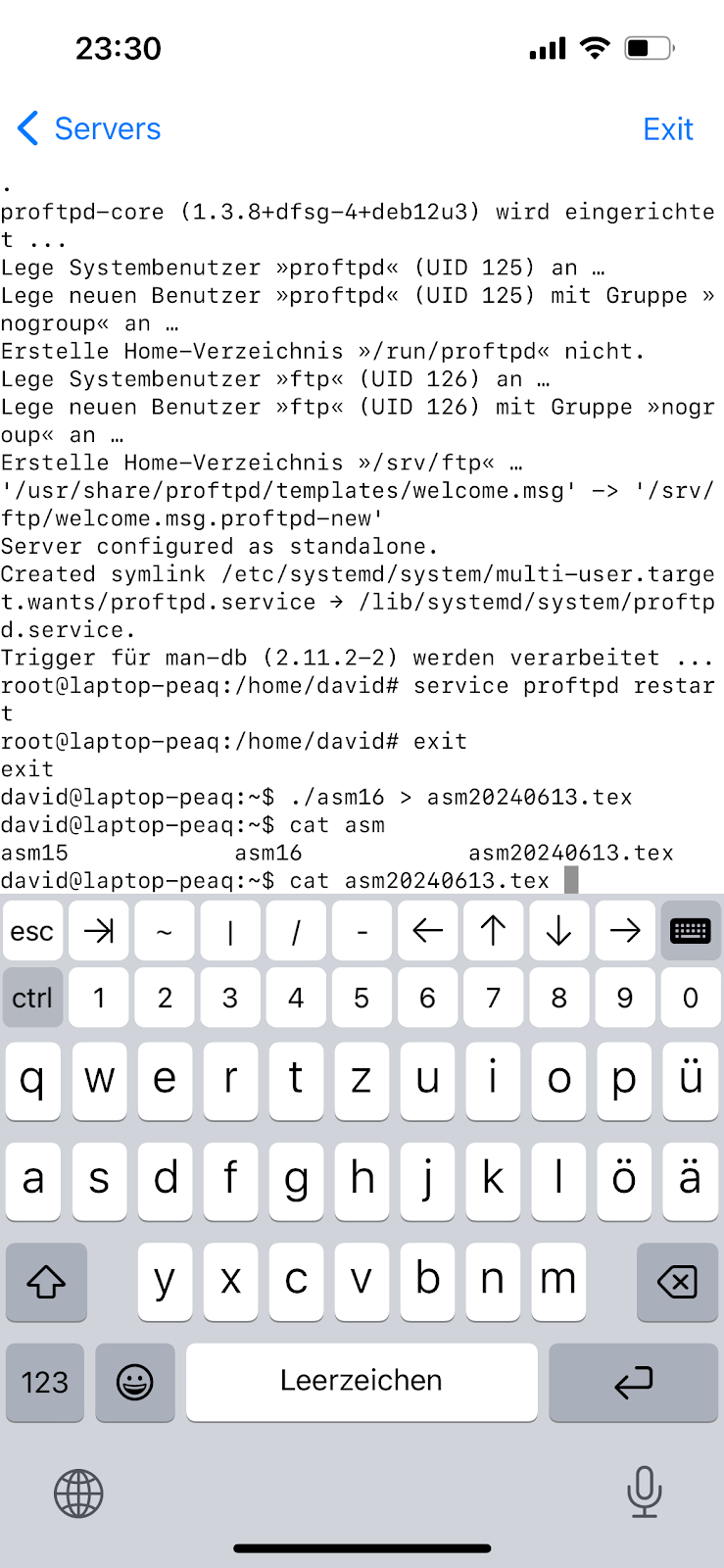

Ok, dann koennen wir anfangen, ssh tut und ftp auch

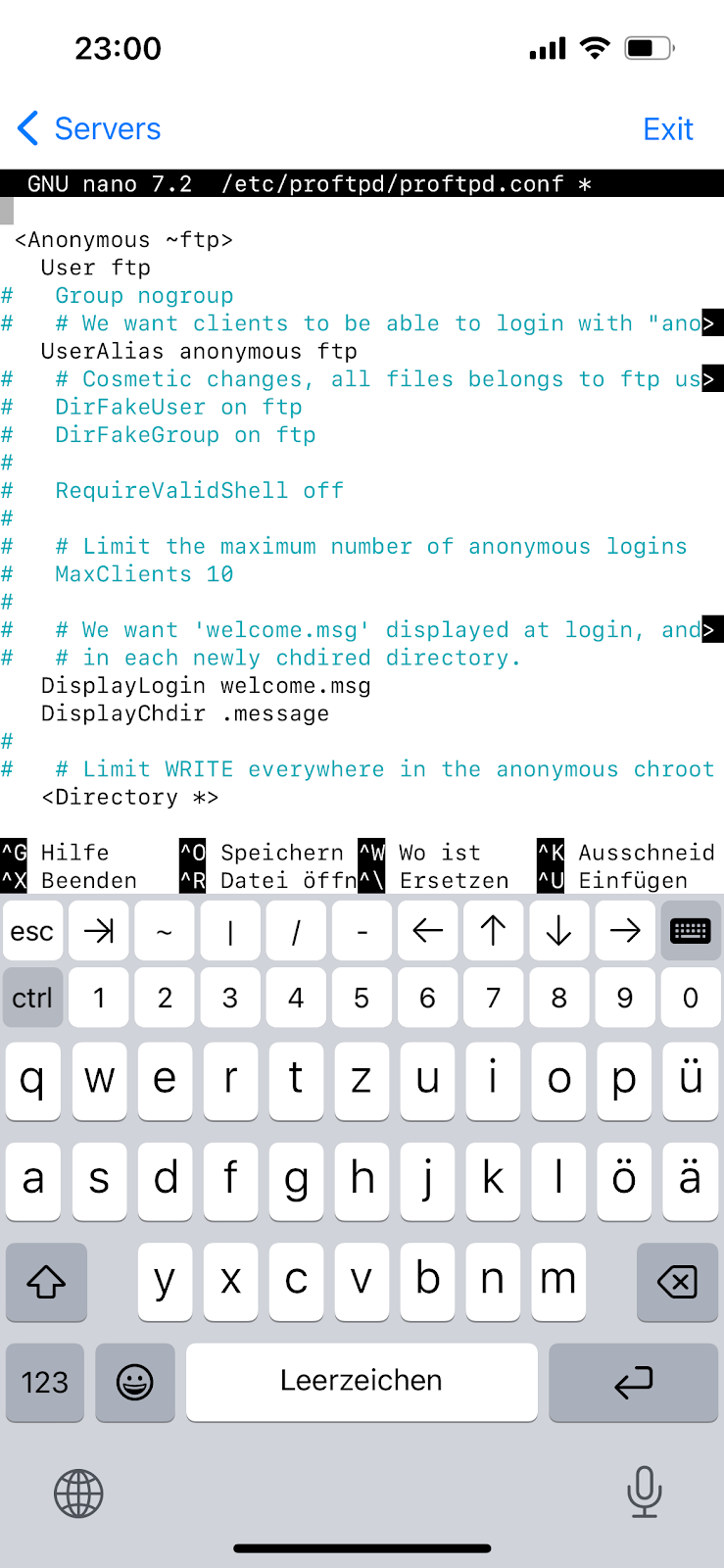

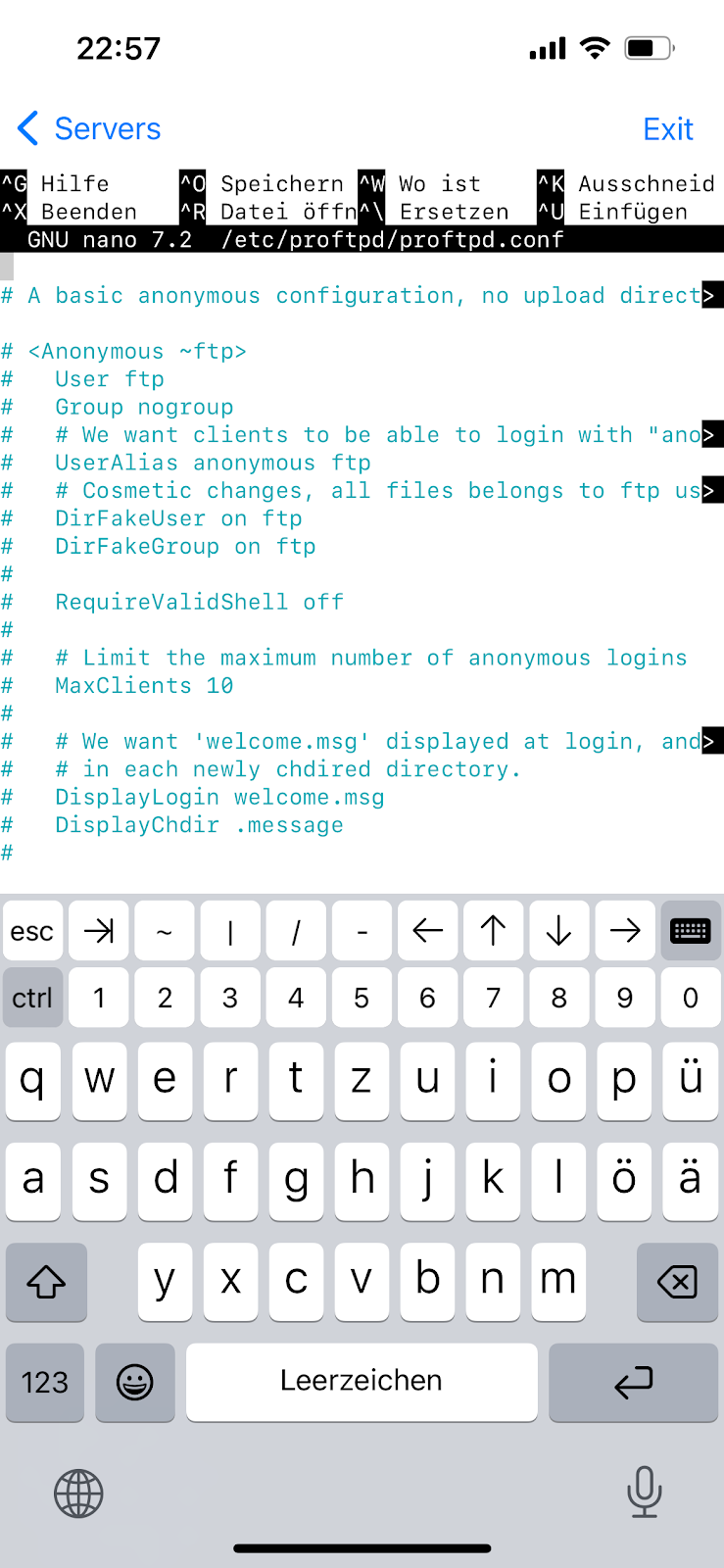

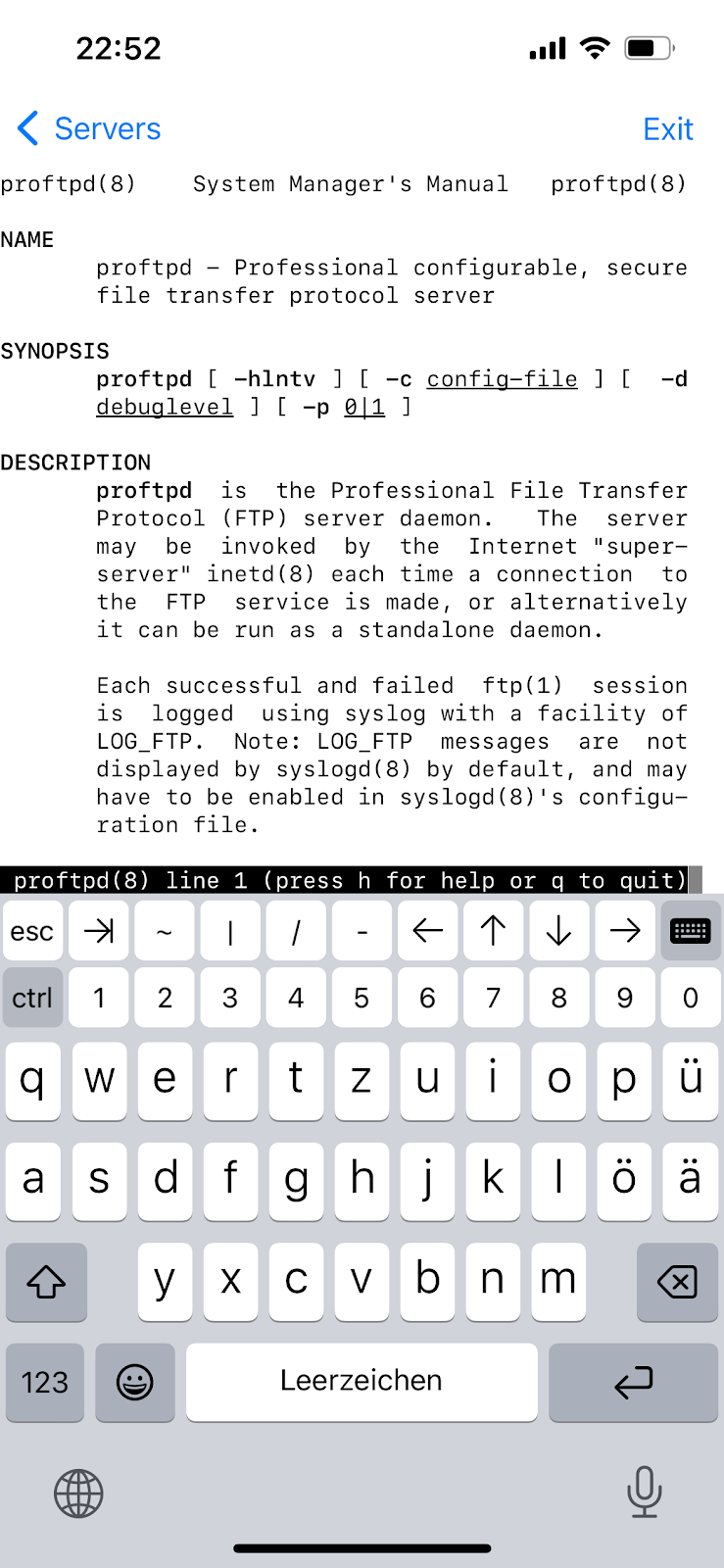

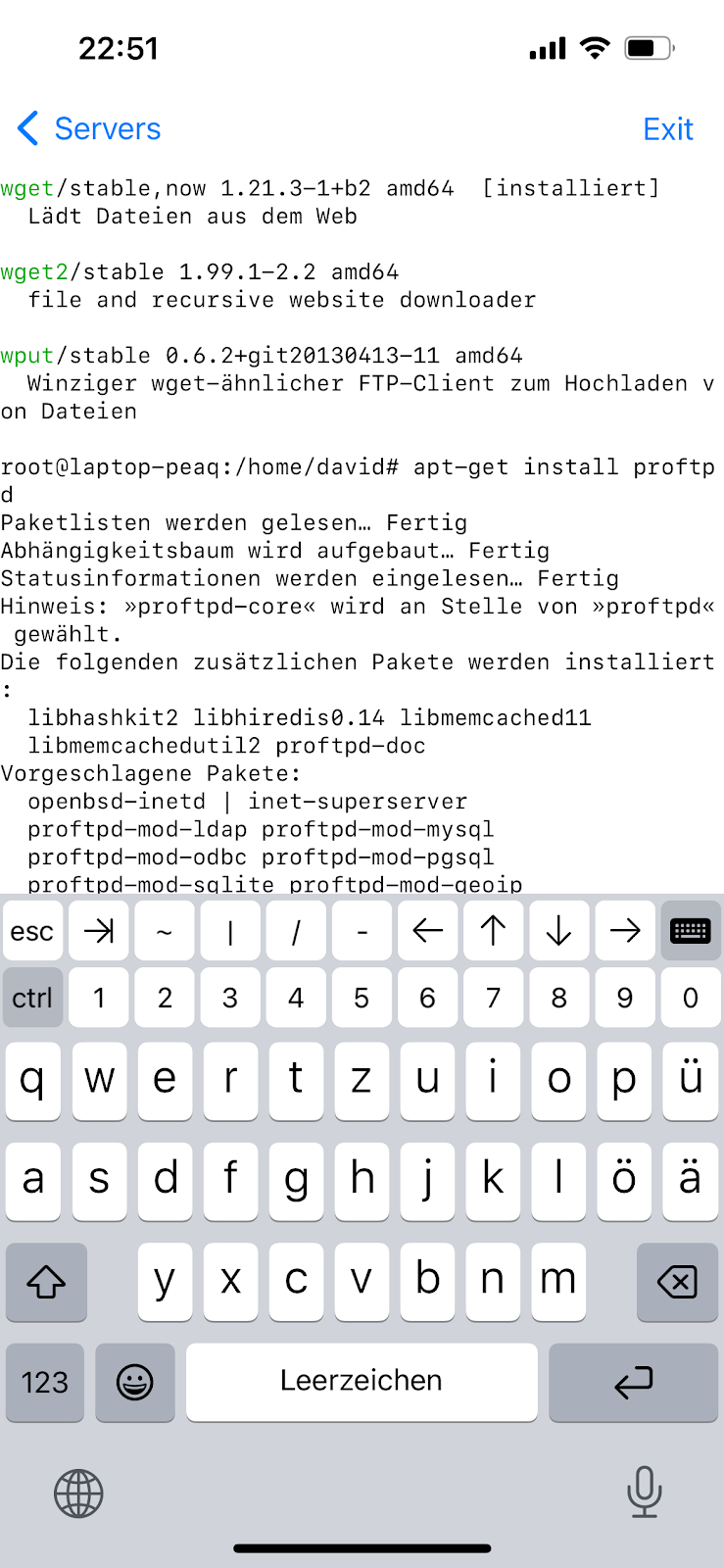

Ok proftpd funktioniert natuerlich so wie jeder Server unter Linux. Postfix und co. Die Nutzer die da sind, sind da. Ich hatte mehrfach proftpd aber nie wirklich genutzt. Ich habe jetzt in der manpage nach geschaut. Sie brauchen den anonymes User ftp nicht freischalten

Ich richte einfach auf dem Linux Server einen ftp Server ein. Per ssh natuerlich. Und ich mache einen ftp Client auf das Smartphone. Dazu gebe ich die Ports von ssh und ftp frei. Und gucke ob ich sie aus dem Netz erreiche. Um einen meiner Rechner muss ich mich noch kuemmern. Dann bin ich fertig.

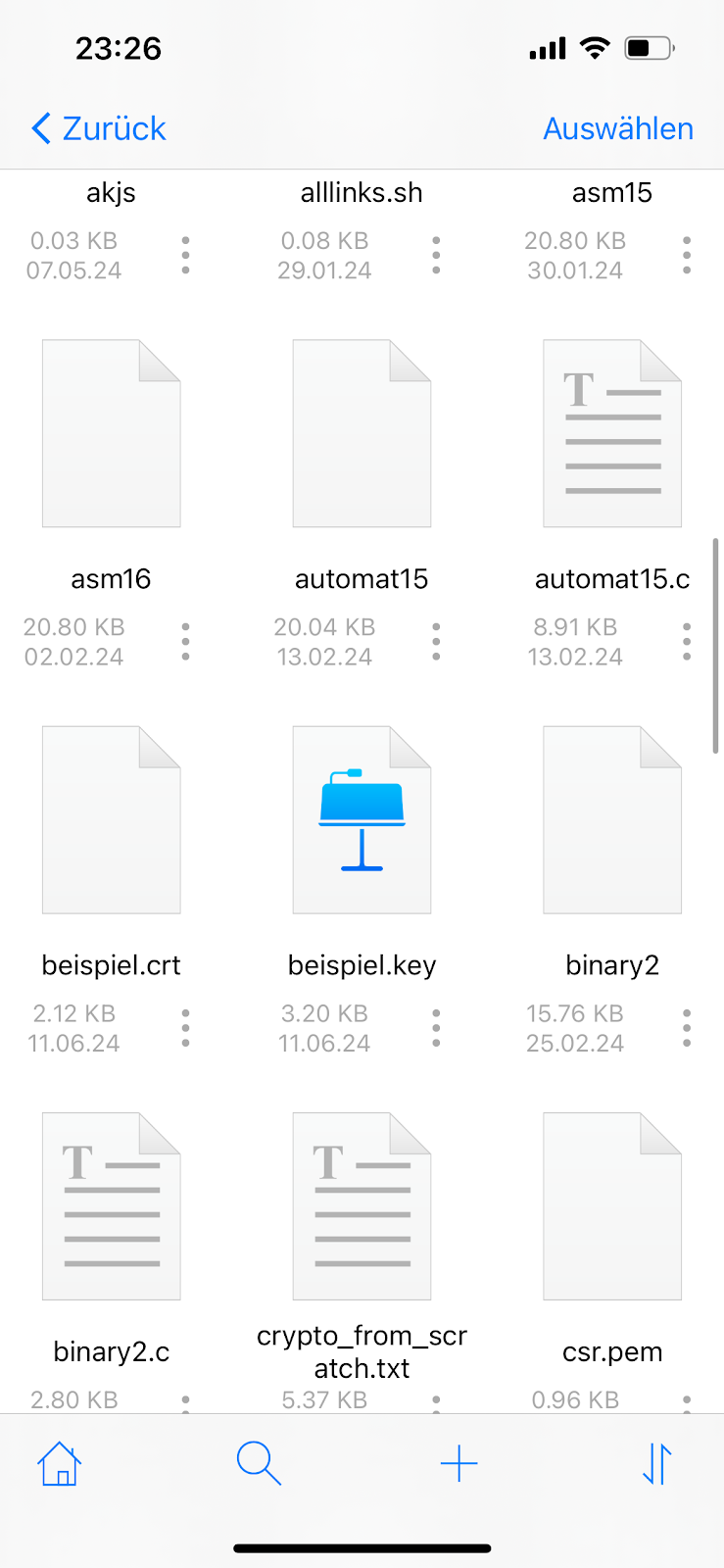

Gcc, c Compiler, pdflatex, gpg, public key encryption, ich meine kde von Linux benutzt gpg, aber das ist egal. Wozu brauche ich das? Ich benutze gpg ueber die Konsole. Webserver, auch OpenSSL, alles. Ich meine mit gpg verschluessele ich Mails zur Not oder lese sie, aber warum sollte ich das nicht auf dem Linux Server selber machen. Mail Inhalt auf den Server da entschluesseln, das ist nur Text. Alles mache ich ueber die Konsole ssh. Auch Ghdl oder sogar gtkwave. Warum nicht das Bild kann ich rueber schicken. Und: ansonsten ist mein iPhone mein sichtgeraet, benutze ich als frontend

Pdflatex, pdftoppm, alles Konsole

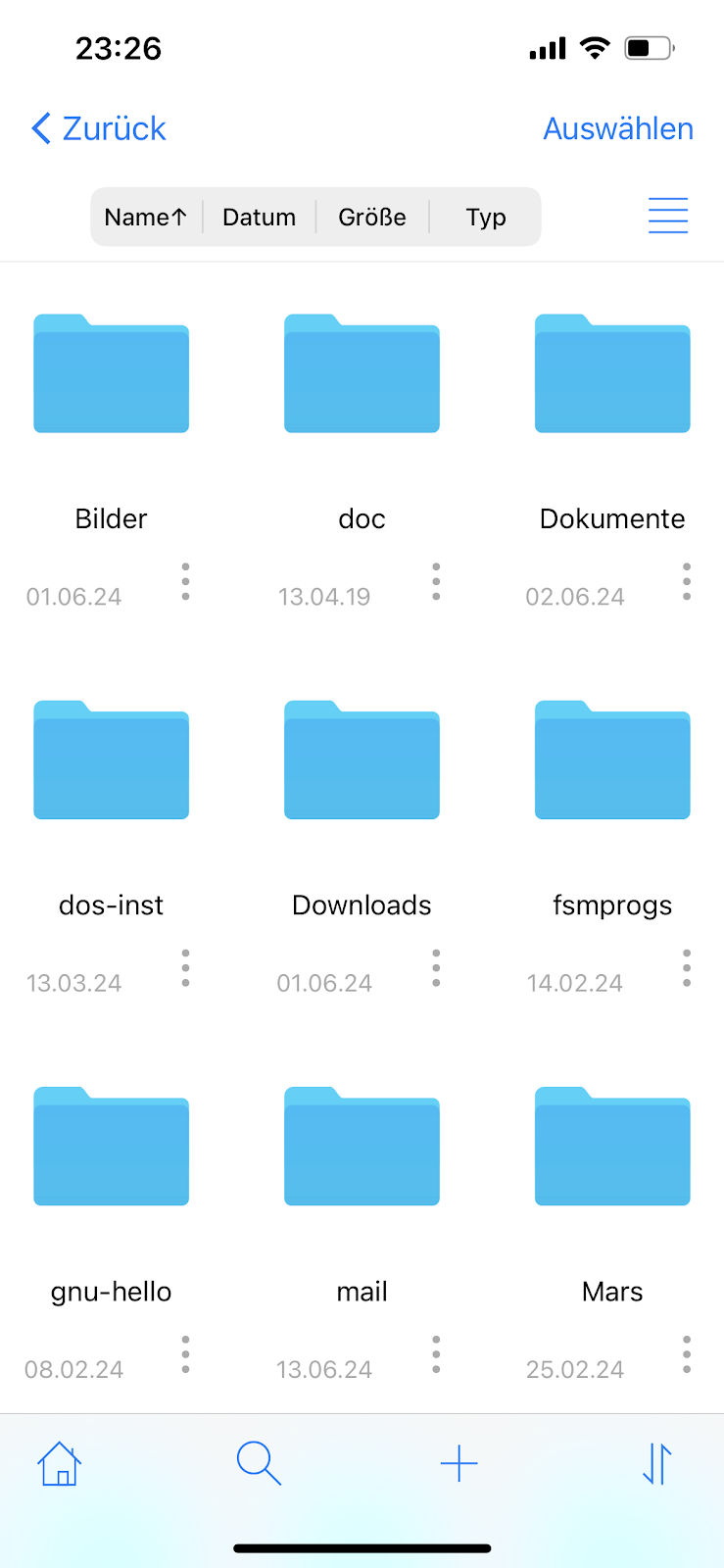

Also, ich habe den vhdl Code, ich mache morgen weiter. Und keine Sorge in meinen Verzeichnissen herrscht Ordnung

--- https://phpbb3.ituenix.de/viewtopic.php?p=2504\&sid=fe31b12ff2b3b374eaca692913acc42d#p2504

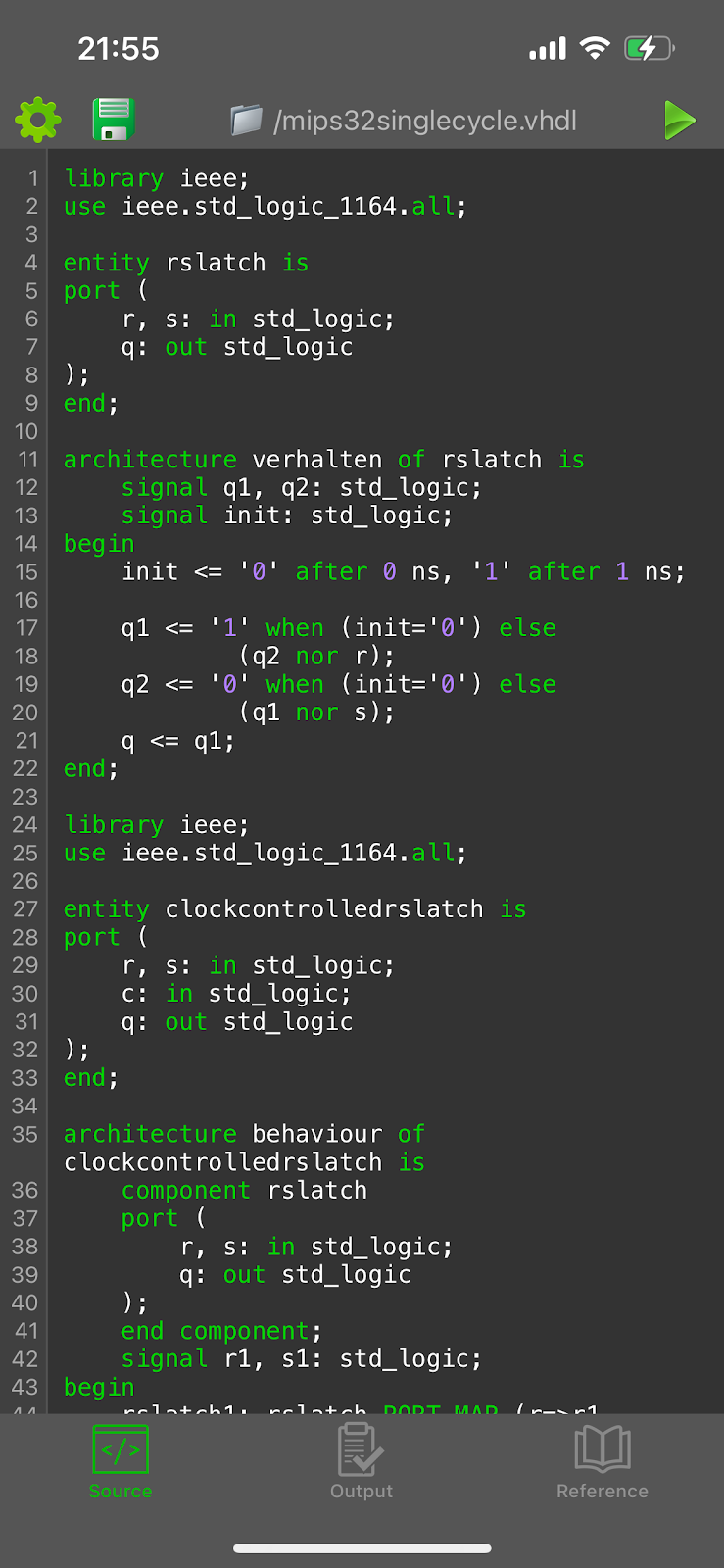

library ieee;

use ieee.std_logic_1164.all;

entity rslatch is

port (

r, s: in std_logic;

q: out std_logic

);

end;

architecture verhalten of rslatch is

signal q1, q2: std_logic;

signal init: std_logic;

begin

init <= '0' after 0 ns, '1' after 1 ns;

q1 <= '1' when (init='0') else

(q2 nor r);

q2 <= '0' when (init='0') else

(q1 nor s);

q <= q1;

end;

library ieee;

use ieee.std_logic_1164.all;

entity clockcontrolledrslatch is

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of clockcontrolledrslatch is

component rslatch

port (

r, s: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

rslatch1: rslatch PORT MAP (r=>r1, s=>s1, q=>q);

s1 <= (s and c);

r1 <= (r and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity dlatch is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dlatch is

component clockcontrolledrslatch

port (

r, s: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal r1, s1: std_logic;

begin

clockcontrolledrslatch1: clockcontrolledrslatch PORT MAP (r=>r1, s=>s1, q=>q, c=>c);

s1 <= not d;

r1 <= d;

end;

library ieee;

use ieee.std_logic_1164.all;

entity dmsflipflop is

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end;

architecture behaviour of dmsflipflop is

component dlatch

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d1, d2: std_logic;

signal c1, c2: std_logic;

signal q1, q2: std_logic;

begin

dlatch1: dlatch PORT MAP (d=>d1, c=>c1, q=>q1);

dlatch2: dlatch PORT MAP (d=>d2, c=>c2, q=>q2);

c1 <= c;

c2 <= not c;

d1 <= d;

d2 <= q1;

q <= q2;

end;

library ieee;

use ieee.std_logic_1164.all;

entity flipfloptestbench is

port (

q: out std_logic

);

end;

architecture behaviour of flipfloptestbench is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

signal d, c: std_logic;

begin

dmsflipflop1: dmsflipflop PORT MAP (q=>q, d=>d, c=>c);

c <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns,

'0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns,

'1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d <= '0' after 0 ns, '1' after 150 ns, '0' after 250 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32 is

port (

we: in std_logic;

q: out std_logic_vector (31 downto 0);

d: in std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32 is

component dmsflipflop

port (

d: in std_logic;

c: in std_logic;

q: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

dmsflipflop1: dmsflipflop PORT MAP (q=>q(i), d=>d(i), c=>we);

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity reg32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of reg32testbench is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (31 downto 0);

signal we: std_logic;

begin

reg32a: reg32 PORT MAP (d=>d, q=>q, we=>we);

d(0) <= '1';

d(1) <= '0';

d(2) <= '1';

d(3) <= '0';

d(4) <= '1';

d(5) <= '0';

d(6) <= '1';

d(7) <= '0';

d(8) <= '1';

d(9) <= '1';

d(10) <= '0';

d(11) <= '1';

d(12) <= '0';

d(13) <= '1';

d(14) <= '0';

d(15) <= '1';

d(16) <= '0';

d(17) <= '1';

d(18) <= '0';

d(19) <= '1';

d(20) <= '0';

d(21) <= '1';

d(22) <= '0';

d(23) <= '1';

d(24) <= '0';

d(25) <= '1';

d(26) <= '0';

d(27) <= '1';

d(28) <= '0';

d(29) <= '1';

d(30) <= '0';

d(31) <= '1';

we <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32 is

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32 is

begin

-- 00000

b (0) <= not a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 00001

b (1) <= not a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 00010

b (2) <= not a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 00011

b (3) <= not a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 00100

b (4) <= not a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 00101

b (5) <= not a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 00110

b (6) <= not a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 00111

b (7) <= not a (4) and not a (3) and a (2) and a (1) and a (0);

-- 01000

b (8) <= not a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 01001

b (9) <= not a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 01010

b (10) <= not a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 01011

b (11) <= not a (4) and a (3) and not a (2) and a (1) and a (0);

-- 01100

b (12) <= not a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 01101

b (13) <= not a (4) and a (3) and a (2) and not a (1) and a (0);

-- 01110

b (14) <= not a (4) and a (3) and a (2) and a (1) and not a (0);

-- 01111

b (15) <= not a (4) and a (3) and a (2) and a (1) and a (0);

-- 10000

b (16) <= a (4) and not a (3) and not a (2) and not a (1) and not a (0);

-- 10001

b (17) <= a (4) and not a (3) and not a (2) and not a (1) and a (0);

-- 10010

b (18) <= a (4) and not a (3) and not a (2) and a (1) and not a (0);

-- 10011

b (19) <= a (4) and not a (3) and not a (2) and a (1) and a (0);

-- 10100

b (20) <= a (4) and not a (3) and a (2) and not a (1) and not a (0);

-- 10101

b (21) <= a (4) and not a (3) and a (2) and not a (1) and a (0);

-- 10110

b (22) <= a (4) and not a (3) and a (2) and a (1) and not a (0);

-- 10111

b (23) <= a (4) and not a (3) and a (2) and a (1) and a (0);

-- 11000

b (24) <= a (4) and a (3) and not a (2) and not a (1) and not a (0);

-- 11001

b (25) <= a (4) and a (3) and not a (2) and not a (1) and a (0);

-- 11010

b (26) <= a (4) and a (3) and not a (2) and a (1) and not a (0);

-- 11011

b (27) <= a (4) and a (3) and not a (2) and a (1) and a (0);

-- 11100

b (28) <= a (4) and a (3) and a (2) and not a (1) and not a (0);

-- 11101

b (29) <= a (4) and a (3) and a (2) and not a (1) and a (0);

-- 11110

b (30) <= a (4) and a (3) and a (2) and a (1) and not a (0);

-- 11111

b (31) <= a (4) and a (3) and a (2) and a (1) and a (0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity addressdecoder5to32testbench is

port (

q: out std_logic_vector (31 downto 0)

);

end;

architecture behaviour of addressdecoder5to32testbench is

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal d: std_logic_vector (4 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (b=>q, a=>d);

d (0) <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns, '1' after 170 ns, '0' after 180 ns, '1' after 190 ns, '0' after 200 ns, '1' after 210 ns, '0' after 220 ns, '1' after 230 ns, '0' after 240 ns, '1' after 250 ns, '0' after 260 ns, '1' after 270 ns, '0' after 280 ns, '1' after 290 ns, '0' after 300 ns, '1' after 310 ns;

d (1) <= '0' after 0 ns, '1' after 20 ns, '0' after 40 ns, '1' after 60 ns, '0' after 80 ns, '1' after 100 ns, '0' after 120 ns, '1' after 140 ns, '0' after 160 ns, '1' after 180 ns, '0' after 200 ns, '1' after 220 ns, '0' after 240 ns, '1' after 260 ns, '0' after 280 ns, '1' after 300 ns, '0' after 320 ns, '1' after 340 ns;

d (2) <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns, '1' after 120 ns, '0' after 160 ns, '1' after 200 ns, '0' after 240 ns, '1' after 280 ns, '0' after 320 ns, '1' after 360 ns;

d (3) <= '0' after 0 ns, '1' after 80 ns, '0' after 160 ns, '1' after 240 ns, '0' after 320 ns, '1' after 400 ns;

d (4) <= '0' after 0 ns, '1' after 160 ns;

end;

library ieee;

use ieee.std_logic_1164.all;

entity registerset32x32 is

port (

writereg: in std_logic_vector (4 downto 0);

readreg1: in std_logic_vector (4 downto 0);

readreg2: in std_logic_vector (4 downto 0);

readport1: out std_logic_vector (31 downto 0);

readport2: out std_logic_vector (31 downto 0);

writeport: in std_logic_vector (31 downto 0);

we: in std_logic

);

end;

architecture behaviour of registerset32x32 is

component reg32

port (

d: in std_logic_vector (31 downto 0);

we: in std_logic;

q: out std_logic_vector (31 downto 0)

);

end component;

component addressdecoder5to32

port (

a: in std_logic_vector (4 downto 0);

b: out std_logic_vector (31 downto 0)

);

end component;

signal writereg1: std_logic_vector (31 downto 0);

begin

addressdecoder5to32a: addressdecoder5to32 PORT MAP (a=>writereg, b=>writereg1);

l1:

for i in 0 to 31 generate

reg32a: reg32 PORT MAP (we=>writereg1(i),d=>writeport,q=>readport1); -- WARNING - WARNING

end generate;

end;